# MC68000 and MC68EC000 Instruction Set Summary

| Mnemonic    | Description                                       |  |  |  |

|-------------|---------------------------------------------------|--|--|--|

| ABCD        | Add Decimal with Extend                           |  |  |  |

| ADD         | Add                                               |  |  |  |

| ADDA        | Add Address                                       |  |  |  |

| ADDI        | Add Immediate                                     |  |  |  |

| ADDQ        | Add Quick                                         |  |  |  |

| ADDX        | Add with Extend                                   |  |  |  |

| AND         | Logical AND                                       |  |  |  |

| ANDI        | Logical AND Immediate                             |  |  |  |

| ANDI to CCR | AND Immediate to Condition Code Register          |  |  |  |

| ANDI to SR  | AND Immediate to Status Register                  |  |  |  |

| ASL, ASR    | Arithmetic Shift Left and Right                   |  |  |  |

| Bcc         | Branch Conditionally                              |  |  |  |

| BCHG        | Test Bit and Change                               |  |  |  |

| BCLR        | Test Bit and Clear                                |  |  |  |

| BRA         | Branch                                            |  |  |  |

| BSET        | Test Bit and Set                                  |  |  |  |

| BSR         | Branch to Subroutine                              |  |  |  |

| BTST        | Test Bit                                          |  |  |  |

| CHK         | Check Register Against Bound                      |  |  |  |

| CLR         | Clear                                             |  |  |  |

| CMP         | Compare                                           |  |  |  |

| CMPA        | Compare Address                                   |  |  |  |

| CMPI        | Compare Immediate                                 |  |  |  |

| СМРМ        | Compare Memory to Memory                          |  |  |  |

| DBcc        | Test Condition, Decrement, and Branch             |  |  |  |

| DIVS        | Signed Divide                                     |  |  |  |

| DIVU        | Unsigned Divide                                   |  |  |  |

| EOR         | Logical Exclusive-OR                              |  |  |  |

| EORI        | Logical Exclusive-OR Immediate                    |  |  |  |

| EORI to CCR | Exclusive-OR Immediate to Condition Code Register |  |  |  |

| EORI to SR  | Exclusive-OR Immediate to Status Register         |  |  |  |

| EXG         | Exchange Registers                                |  |  |  |

| EXT         | Sign Extend                                       |  |  |  |

| ILLEGAL     | Take Illegal Instruction Trap                     |  |  |  |

| JMP         | Jump                                              |  |  |  |

| JSR         | Jump to Subroutine                                |  |  |  |

# MC68000 and MC68EC000 Instruction Set Summary (Continued)

| Mnemonic     | Description                                       |

|--------------|---------------------------------------------------|

| LEA          | Load Effective Address                            |

| LINK         | Link and Allocate                                 |

| LSL, LSR     | Logical Shift Left and Right                      |

| MOVE         | Move                                              |

| MOVEA        | Move Address                                      |

| MOVE to CCR  | Move to Condition Code Register                   |

| MOVE from SR | Move from Status Register                         |

| MOVE to SR   | Move to Status Register                           |

| MOVE USP     | Move User Stack Pointer                           |

| MOVEM        | Move Multiple Registers                           |

| MOVEP        | Move Peripheral                                   |

| MOVEQ        | Move Quick                                        |

| MULS         | Signed Multiply                                   |

| MULU         | Unsigned Multiply                                 |

| NBCD         | Negate Decimal with Extend                        |

| NEG          | Negate                                            |

| NEGX         | Negate with Extend                                |

| NOP          | No Operation                                      |

| NOT          | Logical Complement                                |

| OR           | Logical Inclusive-OR                              |

| ORI          | Logical Inclusive-OR Immediate                    |

| ORI to CCR   | Inclusive-OR Immediate to Condition Code Register |

| ORI to SR    | Inclusive-OR Immediate to Status Register         |

| PEA          | Push Effective Address                            |

| RESET        | Reset External Devices                            |

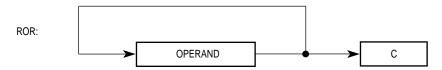

| ROL, ROR     | Rotate Left and Right                             |

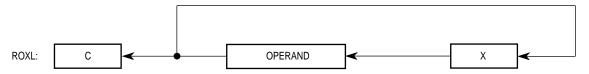

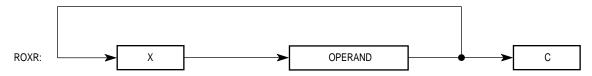

| ROXL, ROXR   | Rotate with Extend Left and Right                 |

| RTE          | Return from Exception                             |

| RTR          | Return and Restore                                |

| RTS          | Return from Subroutine                            |

| SBCD         | Subtract Decimal with Extend                      |

| Scc          | Set Conditionally                                 |

| STOP         | Stop                                              |

| SUB          | Subtract                                          |

| SUBA         | Subtract Address                                  |

| SUBI         | Subtract Immediate                                |

| SUBQ         | Subtract Quick                                    |

| SUBX         | Subtract with Extend                              |

| SWAP         | Swap Register Words                               |

| TAS          | Test Operand and Set                              |

| TRAP         | Trap                                              |

| TRAPV        | Trap on Overflow                                  |

| TST          | Test Operand                                      |

| UNLK         | Unlink                                            |

# **Operands and Notational Conventions**

|                          | Operands                                                              |

|--------------------------|-----------------------------------------------------------------------|

| An                       | Any Address Register n (example: A3 is address register 3)            |

| Dn                       | Any Data Register n (example: D5 is data register 5)                  |

| Rn                       | Any data or address registerData register D7–D0, used during compare. |

| PC                       | Program counter                                                       |

| SR                       | Status register                                                       |

| CCR                      | Condition codes register (low order byte of SR)                       |

| SSP                      | Supervisor stack pointer                                              |

| USP                      | User stack pointer                                                    |

| SP                       | Active stack pointer (same as A7)                                     |

| Х                        | Extend flag of the CCR                                                |

| N                        | Negative flag of the CCR                                              |

| Z                        | Zero flag of the CCR                                                  |

| V                        | Overflow flag of the CCR                                              |

| С                        | Carry flag of the CCR                                                 |

| Immediate data           | Immediate data for the instruction                                    |

| d                        | Address displacement                                                  |

| Source                   | Source contents                                                       |

| Destination              | Destination contents                                                  |

| Vector                   | Location of exception vector                                          |

| ea                       | Any valid effective address                                           |

|                          | Notational Conventions                                                |

| +                        | Arithmetic addition or postincrement indicator                        |

| _                        | Arithmetic subtraction or predecrement indicator                      |

| ×                        | Arithmetic multiplication                                             |

| ÷                        | Arithmetic division or conjunction symbol                             |

| ~                        | Invert; operand is logically complemented.                            |

| Λ                        | Logical AND                                                           |

| V                        | Logical OR                                                            |

| $\oplus$                 | Logical exclusive OR                                                  |

| $\rightarrow$            | Source operand is moved to destination operand.                       |

| $\leftarrow \rightarrow$ | Two operands are exchanged.                                           |

# **INSTRUCTION NAME** ASSEMBLER SYNTAX SIZE ATTRIBUTE-TEXT DESCRIPTION OF INSTRUCTION OPERATION EFFECTS ON CONDITION CODES INSTRUCTION FORMAT — SPECIFIES THE BIT PATTERN-AND FIELDS OF THE "OPCODE" WORD DEFINITIONS AND ALLOWED VALUES FOR THE **INSTRUCTION FIELDS**

# **ABCD**

Add Decim

Operation: Source10 + Destinat

**Assembler** ABCD Dy,Dx

**Syntax:** ABCD - (Ay), - (Ax)

**Attributes:** Size = (Byte)

Description: Adds the source operand to and stores the result in the destinatio coded decimal arithmetic. The opnumbers, can be addressed in two

- Data Register to Data Regist ters specified in the instructi

- 2. Memory to Memory: The op dressing mode using the ad

This operation is a byte operation on

### **Condition Codes:**

| X | Ν | Z | V | С |

|---|---|---|---|---|

| * | U | * | U | * |

X — Set the same as the carry bi

N — Undefined.

Z — Cleared if the result is nonze.

V — Undefined.

C — Set if a decimal carry was q

Normally, the Z condition co the start of an operation. / results upon completion of

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10     | 9  |

|----|----|----|----|----|--------|----|

| 1  | 1  | 0  | 0  | RE | GISTER | Rx |

### **Instruction Fields:**

Register Rx field—Specifies the d' If R/M = 0, specifies a data reg

If R/M = 1, specifies an address

R/M field—Specifies the operand

0 — The operation is data regis

1 — The operation is memory to

Register Ry field—Specifies the If R/M = 0, specifies a data reg

If R/M = 1, specifies an address

# **ABCD**

### **Add Decimal with Extend**

**ABCD**

**Operation:** Source10 + Destination10 +  $X \rightarrow$  Destination

**Assembler** ABCD Dy,Dx

**Syntax:** ABCD - (Ay), - (Ax)

**Attributes:** Size = (Byte)

**Description:** Adds the source operand to the destination operand along with the extend bit, and stores the result in the destination location. The addition is performed using binary-coded decimal arithmetic. The operands, which are packed binary-coded decimal numbers, can be addressed in two different ways:

- 1. Data Register to Data Register: The operands are contained in the data registers specified in the instruction.

- Memory to Memory: The operands are addressed with the predecrement addressing mode using the address registers specified in the instruction.

This operation is a byte operation only.

### **Condition Codes:**

| Χ | Ν | Z | V | С |

|---|---|---|---|---|

| * | U | * | U | * |

X — Set the same as the carry bit.

N — Undefined.

Z — Cleared if the result is nonzero; unchanged otherwise.

V — Undefined.

C — Set if a decimal carry was generated; cleared otherwise.

#### **NOTE**

Normally, the Z condition code bit is set via programming before the start of an operation. This allows successful tests for zero results upon completion of multiple-precision operations.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3   | 2    | 1      | 0       |

|----|----|----|----|----|----|----|---|---|---|---|---|-----|------|--------|---------|

| 1  | 1  | 0  | 0  |    |    | Rx | 1 | 0 | 0 | 0 | 0 | R/M | I NE | GISTER | . IT. V |

### **Instruction Fields:**

Register Rx field—Specifies the destination register.

If R/M = 0, specifies a data register.

If R/M = 1, specifies an address register for the predecrement addressing mode.

R/M field—Specifies the operand addressing mode.

0 — The operation is data register to data register.

1 — The operation is memory to memory.

Register Ry field—Specifies the source register.

If R/M = 0, specifies a data register.

If R/M = 1, specifies an address register for the predecrement addressing mode.

**Operation:** Source + Destination → Destination

Assembler ADD < ea > ,Dn Syntax: ADD Dn, < ea >

**Attributes:** Size = (Byte, Word, Long)

**Description:** Adds the source operand to the destination operand using binary addition and stores the result in the destination location. The size of the operation may be specified as byte, word, or long. The mode of the instruction indicates which operand is the source and which is the destination, as well as the operand size.

### **Condition Codes:**

| X | Ν | Z | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

X — Set the same as the carry bit.

N — Set if the result is negative; cleared otherwise.

Z — Set if the result is zero; cleared otherwise.

V — Set if an overflow is generated; cleared otherwise.

C — Set if a carry is generated; cleared otherwise.

### **Instruction Format:**

|   | 15 | 14 | 13 | 12 | 11 | 10       | 9        | 8 | 7         | 6 | 5 | 4    | 3      | 2     | 1      | 0 |

|---|----|----|----|----|----|----------|----------|---|-----------|---|---|------|--------|-------|--------|---|

| ſ | 1  | 1  | 0  | 1  |    | PECIETEI | <b>.</b> | , | OPMODE    | _ |   | EFF  | ECTIVE | ADDRE | SS     |   |

|   | '  | '  | "  | '  | '  | (LGISTLI | `        | ` | JE IVIODI | _ |   | MODE |        | R     | EGISTE | R |

### **Instruction Fields:**

Register field—Specifies any of the eight data registers.

### Opmode field

| Byte | Word | Long | Operation                        |

|------|------|------|----------------------------------|

| 000  | 001  | 010  | $<$ ea $>$ + Dn $\rightarrow$ Dn |

| 100  | 101  | 110  | $Dn + < ea > \rightarrow < ea >$ |

Effective Address field—Determines addressing mode.

a. If the location specified is a source operand, all addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An*                     | 001  | reg. number:An |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| – (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | 111  | 100      |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | 111  | 010      |

| (d <sub>8</sub> ,PC,Xn) | 111  | 011      |

b. If the location specified is a destination operand, only memory alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | _    | _              |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

### **NOTE**

The Dn mode is used when the destination is a data register; the destination < ea > mode is invalid for a data register.

ADDA is used when the destination is an address register. ADDI and ADDQ are used when the source is immediate data. Most assemblers automatically make this distinction.

<sup>\*</sup>Word and long only

# ADDA Add Address ADDA

**Operation:** Source + Destination → Destination

**Assembler**

**Syntax:** ADDA < ea > , An

**Attributes:** Size = (Word, Long)

**Description:** Adds the source operand to the destination address register and stores the result in the address register. The size of the operation may be specified as word or long. The entire destination address register is used regardless of the operation size.

### **Condition Codes:**

Not affected.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10       | 9 | 8       | 7      | 6 | 5                        | 4    | 3 | 2 | 1      | 0 |

|----|----|----|----|----|----------|---|---------|--------|---|--------------------------|------|---|---|--------|---|

| 1  | 1  | 0  | 1  | _  | PECISTER | , | <b></b> | ODMODE |   | OPMODE EFFECTIVE ADDRESS |      |   |   | SS     |   |

| '  | '  | 0  | '  |    | KEGISTER |   | ,       | JEMODI | = |                          | MODE |   | R | EGISTE | R |

### **Instruction Fields:**

Register field—Specifies any of the eight address registers. This is always the destination.

Opmode field—Specifies the size of the operation.

011—Word operation; the source operand is sign-extended to a long operand and the operation is performed on the address register using all 32 bits.

111— Long operation.

Effective Address field—Specifies the source operand. All addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An                      | 001  | reg. number:An |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | 111  | 100      |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | 111  | 010      |

| (d <sub>8</sub> ,PC,Xn) | 111  | 011      |

# ADDI Add Immediate ADDI

**Operation:** Immediate Data + Destination → Destination

**Assembler**

**Syntax:** ADDI # < data > , < ea >

**Attributes:** Size = (Byte, Word, Long)

**Description:** Adds the immediate data to the destination operand and stores the result in the destination location. The size of the operation may be specified as byte, word, or long. The size of the immediate data matches the operation size.

### **Condition Codes:**

| Χ | Ν | Z | V | С |  |  |

|---|---|---|---|---|--|--|

| * | * | * | * | * |  |  |

X — Set the same as the carry bit.

N — Set if the result is negative; cleared otherwise.

Z — Set if the result is zero; cleared otherwise.

V — Set if an overflow is generated; cleared otherwise.

C — Set if a carry is generated; cleared otherwise.

### **Instruction Format:**

| 15 | 14               | 13 | 12 | 11 | 10 | 9   | 8 | 7   | 6    | 5   | 4      | 3        | 2       | 1      | 0 |     |        |       |    |  |

|----|------------------|----|----|----|----|-----|---|-----|------|-----|--------|----------|---------|--------|---|-----|--------|-------|----|--|

| 0  | _                | _  | _  | 0  | 1  | 1 0 | 4 |     | 1 0  | 1 0 | 0 9175 |          | CIZE    |        |   | EFF | ECTIVE | ADDRE | SS |  |

| "  | "                | "  | "  | 0  | '  | '   | " | ا ا | SIZE |     | MODE   |          | R       | EGISTE | R |     |        |       |    |  |

|    | 16-BIT WORD DATA |    |    |    |    |     |   |     |      |     | 8      | B-BIT BY | TE DATA | 4      |   |     |        |       |    |  |

|    | 32-BIT LONG DATA |    |    |    |    |     |   |     |      |     |        |          |         |        |   |     |        |       |    |  |

### **Instruction Fields:**

Size field—Specifies the size of the operation.

00 — Byte operation

01 — Word operation

10 — Long operation

Effective Address field—Specifies the destination operand. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

Immediate field—Data immediately following the instruction.

If size = 00, the data is the low-order byte of the immediate word.

If size = 01, the data is the entire immediate word.

If size = 10, the data is the next two immediate words.

**Operation:** Immediate Data + Destination → Destination

**Assembler**

Syntax: ADDQ # < data > , < ea > Attributes: Size = (Byte, Word, Long)

**Description:** Adds an immediate value of one to eight to the operand at the destination location. The size of the operation may be specified as byte, word, or long. Word and long operations are also allowed on the address registers. When adding to address registers, the condition codes are not altered, and the entire destination address register is used regardless of the operation size.

### **Condition Codes:**

| Χ | N | Z | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

X — Set the same as the carry bit.

N — Set if the result is negative; cleared otherwise.

Z — Set if the result is zero; cleared otherwise.

V — Set if an overflow occurs; cleared otherwise.

C — Set if a carry occurs; cleared otherwise.

The condition codes are not affected when the destination is an address register.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10   | 9 | 8 | 7   | 6        | 5 | 4    | 3      | 2     | 1      | 0 |

|----|----|----|----|----|------|---|---|-----|----------|---|------|--------|-------|--------|---|

| 0  | 1  | 0  | 1  |    | DATA |   | 0 | SIZ | 7E       |   | EFF  | ECTIVE | ADDRE | SS     |   |

| U  | '  | U  | !  |    | DATA |   | U | 312 | <u> </u> |   | MODE |        | R     | EGISTE | R |

### **Instruction Fields:**

Data field—Three bits of immediate data representing eight values (0 - 7), with the immediate value zero representing a value of eight.

Size field—Specifies the size of the operation.

00— Byte operation

01— Word operation

10— Long operation

Effective Address field—Specifies the destination location. Only alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An*                     | 001  | reg. number:An |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

<sup>\*</sup>Word and Long only.

# ADDX Add Extended ADDX

**Operation:** Source + Destination +  $X \rightarrow$  Destination

**Assembler** ADDX Dy,Dx

**Syntax:** ADDX - (Ay), - (Ax)

**Attributes:** Size = (Byte, Word, Long)

**Description:** Adds the source operand and the extend bit to the destination operand and stores the result in the destination location. The operands can be addressed in two different ways:

- 1. Data register to data register—The data registers specified in the instruction contain the operands.

- 2. Memory to memory—The address registers specified in the instruction address the operands using the predecrement addressing mode.

The size of the operation can be specified as byte, word, or long.

### **Condition Codes:**

| Χ | N | Z | V | С |  |

|---|---|---|---|---|--|

| * | * | * | * | * |  |

- X Set the same as the carry bit.

- N Set if the result is negative; cleared otherwise.

- Z Cleared if the result is nonzero; unchanged otherwise.

- V Set if an overflow occurs; cleared otherwise.

- C Set if a carry is generated; cleared otherwise.

#### NOTE

Normally, the Z condition code bit is set via programming before the start of an operation. This allows successful tests for zero results upon completion of multiple-precision operations.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10          | 9 | 8 | 7 | 6  | 5 | 4 | 3   | 2  | 1      | 0  |

|----|----|----|----|----|-------------|---|---|---|----|---|---|-----|----|--------|----|

| 1  | 1  | 0  | 1  | RE | REGISTER Rx |   | 1 |   | ZE | 0 | 0 | R/M | RE | GISTER | Ry |

#### Instruction Fields:

Register Rx field—Specifies the destination register.

If R/M = 0, specifies a data register.

If R/M = 1, specifies an address register for the predecrement addressing mode.

Size field—Specifies the size of the operation.

00 — Byte operation

01 — Word operation

10 — Long operation

R/M field—Specifies the operand address mode.

- 0 The operation is data register to data register.

- 1 The operation is memory to memory.

Register Ry field—Specifies the source register.

If R/M = 0, specifies a data register.

If R/M = 1, specifies an address register for the predecrement addressing mode.

# AND Logical AND

**Operation:** Source L Destination → Destination

Assembler AND < ea > ,Dn Syntax: AND Dn, < ea >

**Attributes:** Size = (Byte, Word, Long)

**Description:** Performs an AND operation of the source operand with the destination operand and stores the result in the destination location. The size of the operation can be specified as byte, word, or long. The contents of an address register may not be used as an operand.

### **Condition Codes:**

| X | Ν | Z | V | С |

|---|---|---|---|---|

| _ | * | * | 0 | 0 |

X — Not affected.

N — Set if the most significant bit of the result is set; cleared otherwise.

Z — Set if the result is zero; cleared otherwise.

V — Always cleared.

C — Always cleared.

### **Instruction Format:**

| 15 | 14 | 13 | 12  | 11       | 10 | 9        | 8      | 7 | 6 | 5                 | 4 | 3    | 2 | 1 | 0      |   |

|----|----|----|-----|----------|----|----------|--------|---|---|-------------------|---|------|---|---|--------|---|

| 1  | 1  | 0  | _   | DECICTED |    | <b></b>  | OPMODE |   |   | EFFECTIVE ADDRESS |   |      |   |   |        |   |

| 1  | '  | 0  | 0 0 | 0   0    |    | REGISTER |        | ` |   | <u>L</u>          |   | MODE |   | R | EGISTE | R |

### **Instruction Fields:**

Register field—Specifies any of the eight data registers.

### Opmode field

| Byte | Word | Long | Operation                                |

|------|------|------|------------------------------------------|

| 000  | 001  | 010  | $<$ ea $>$ $\Lambda$ Dn $\rightarrow$ Dn |

| 100  | 101  | 110  | Dn $\Lambda$ < ea > $\rightarrow$ < ea > |

Effective Address field—Determines addressing mode.

a. If the location specified is a source operand, only data addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |  |  |  |  |

|-------------------------|------|----------|--|--|--|--|

| (xxx).W                 | 111  | 000      |  |  |  |  |

| (xxx).L                 | 111  | 001      |  |  |  |  |

| # <data></data>         | 111  | 100      |  |  |  |  |

|                         |      |          |  |  |  |  |

|                         |      |          |  |  |  |  |

| (d <sub>16</sub> ,PC)   | 111  | 010      |  |  |  |  |

| (d <sub>8</sub> ,PC,Xn) | 111  | 011      |  |  |  |  |

b. If the location specified is a destination operand, only memory alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | _    | _              |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| – (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

### **NOTE**

The Dn mode is used when the destination is a data register; the destination < ea > mode is invalid for a data register.

Most assemblers use ANDI when the source is immediate data.

# ANDI AND Immediate ANDI

**Operation:** Immediate Data  $\Lambda$  Destination  $\rightarrow$  Destination

**Assembler**

Syntax: ANDI # < data > , < ea > Attributes: Size = (Byte, Word, Long)

**Description:** Performs an AND operation of the immediate data with the destination operand and stores the result in the destination location. The size of the operation can be specified as byte, word, or long. The size of the immediate data matches the operation size.

### **Condition Codes:**

| Χ | Ν | Z | V | С |

|---|---|---|---|---|

| _ | * | * | 0 | 0 |

X — Not affected.

N — Set if the most significant bit of the result is set; cleared otherwise.

Z — Set if the result is zero; cleared otherwise.

V — Always cleared.

C — Always cleared.

### **Instruction Format:**

| 15               | 14 | 13 | 12    | 11 | 10 | 9 | 8 | 7   | 6          | 5    | 4    | 3        | 2       | 1      | 0   |        |       |    |  |

|------------------|----|----|-------|----|----|---|---|-----|------------|------|------|----------|---------|--------|-----|--------|-------|----|--|

| 0                | 0  | 0  | 0     | 0  | 0  | 1 | 4 | 1 0 |            | SIZE |      | SIZE     |         |        | EFF | ECTIVE | ADDRE | SS |  |

| 0                |    |    | 0   0 | 0  | "  |   | " | 31, | <b>Z</b> E |      | MODE |          | R       | EGISTE | R   |        |       |    |  |

| 16-BIT WORD DATA |    |    |       |    |    |   |   |     |            |      | 8    | B-BIT BY | TE DATA | 4      |     |        |       |    |  |

| 32-BIT LONG DATA |    |    |       |    |    |   |   |     |            |      |      |          |         |        |     |        |       |    |  |

#### Instruction Fields:

Size field—Specifies the size of the operation.

00 — Byte operation

01 — Word operation

10 — Long operation

Effective Address field—Specifies the destination operand. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

Immediate field—Data immediately following the instruction.

If size = 00, the data is the low-order byte of the immediate word.

If size = 01, the data is the entire immediate word.

If size = 10, the data is the next two immediate words.

# ANDI to CCR

### **AND Immediate to Condition Codes**

**Operation:** Source  $\Lambda CCR \rightarrow CCR$

**Assembler**

Syntax: ANDI # < data > ,CCR

**Attributes:** Size = (Byte)

**Description:** Performs an AND operation of the immediate operand with the condition codes and stores the result in the low-order byte of the status register.

### **Condition Codes:**

| Χ | Ν | Z | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

X — Cleared if bit 4 of immediate operand is zero; unchanged otherwise.

N — Cleared if bit 3 of immediate operand is zero; unchanged otherwise.

Z — Cleared if bit 2 of immediate operand is zero; unchanged otherwise.

V — Cleared if bit 1 of immediate operand is zero; unchanged otherwise.

C — Cleared if bit 0 of immediate operand is zero; unchanged otherwise.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4        | 3       | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|----------|---------|---|---|---|

| 0  | 0  | 0  | 0  | 0  | 0  | 1 | 0 | 0 | 0 | 1 | 1        | 1       | 1 | 0 | 0 |

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |   |   | ; | 8-BIT BY | TE DATA | 4 |   |   |

ANDI to SR

# AND Immediate to the Status Register (Privileged Instruction)

ANDI to SR

**Operation:** Source  $\Lambda$  SR  $\rightarrow$  SR

**Assembler**

**Syntax:** ANDI # < data >,SR

**Attributes:** Size = (Word)

**Description:** Performs an AND operation of the immediate operand with the status register and stores the result in the status register.

### **Condition Codes:**

| Χ | Ν | Z | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

X — Cleared if bit 4 of immediate operand is zero; unchanged otherwise.

N — Cleared if bit 3 of immediate operand is zero; unchanged otherwise.

Z — Cleared if bit 2 of immediate operand is zero; unchanged otherwise.

V — Cleared if bit 1 of immediate operand is zero; unchanged otherwise.

C — Cleared if bit 0 of immediate operand is zero; unchanged otherwise.

### **Instruction Format:**

| 15 | 14               | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0                | 0  | 0  | 0  | 0  | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

|    | 16—BIT WORD DATA |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

# ASL, ASR

### **Arithmetic Shift**

ASL, ASR

**Operation:** Destination Shifted By Count → Destination

**Assembler** ASd Dx,Dy

**Syntax:** ASd # < data > ,Dy

ASd < ea >

where d is direction, L or R

Attributes: Size = (Byte, Word, Long)

**Description:** Arithmetically shifts the bits of the operand in the direction (L or R) specified. The carry bit receives the last bit shifted out of the operand. The shift count for the shifting of a register may be specified in two different ways:

- 1. Immediate—The shift count is specified in the instruction (shift range, 1 8).

- 2. Register—The shift count is the value in the data register specified in instruction modulo 64.

The size of the operation can be specified as byte, word, or long. An operand in memory can be shifted one bit only, and the operand size is restricted to a word.

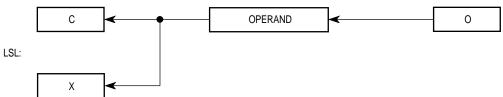

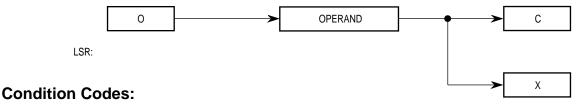

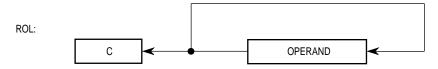

For ASL, the operand is shifted left; the number of positions shifted is the shift count. Bits shifted out of the high-order bit go to both the carry and the extend bits; zeros are shifted into the low-order bit. The overflow bit indicates if any sign changes occur during the shift.

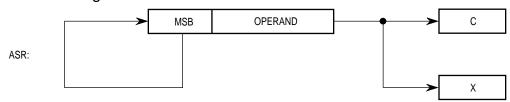

C OPERAND O

For ASR, the operand is shifted right; the number of positions shifted is the shift count. Bits shifted out of the low-order bit go to both the carry and the extend bits; the sign bit (MSB) is shifted into the high-order bit.

#### **Condition Codes:**

| Χ | Ν | Z | V | С |

|---|---|---|---|---|

| * | * | * | * | * |

- X Set according to the last bit shifted out of the operand; unaffected for a shift count of zero.

- N Set if the most significant bit of the result is set; cleared otherwise.

- Z Set if the result is zero; cleared otherwise.

- V Set if the most significant bit is changed at any time during the shift operation; cleared otherwise.

- C Set according to the last bit shifted out of the operand; cleared for a shift count of zero.

### **Arithmetic Shift**

ASL, ASR

### **Instruction Format (Register Shifts):**

| 15 | 14 | 13 | 12 | 11 | 10                 | 9 | 8  | 7  | 6  | 5   | 4 | 3 | 2 | 1      | 0   |

|----|----|----|----|----|--------------------|---|----|----|----|-----|---|---|---|--------|-----|

| 1  | 1  | 1  | 0  | F  | COUNT/<br>REGISTER | ₹ | dr | SI | ZE | i/r | 0 | 0 | R | EGISTE | K I |

### **Instruction Fields (Register Shifts):**

Count/Register field—Specifies shift count or register that contains the shift count:

If i/r = 0, this field contains the shift count. The values 1 - 7 represent counts of 1 - 7; a value of zero represents a count of eight.

If i/r = 1, this field specifies the data register that contains the shift count (modulo 64).

dr field—Specifies the direction of the shift.

0 — Shift right

1 — Shift left

Size field—Specifies the size of the operation.

00 — Byte operation

01 — Word operation

10 — Long operation

i/r field

If i/r = 0, specifies immediate shift count.

If i/r = 1, specifies register shift count.

Register field—Specifies a data register to be shifted.

# Instruction Format (Memory Shifts):

|   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7 | 6 | 5 | 4    | 3      | 2     | 1      | 0 |

|---|----|----|----|----|----|----|---|----|---|---|---|------|--------|-------|--------|---|

| ſ | 1  | 1  | 1  | 0  | 0  | 0  | 0 | dr | 1 | 1 |   | EF   | ECTIVE | ADDRE | SS     |   |

|   | '  | '  | '  | 0  | "  | "  | " | dr | ' | ' |   | MODE |        | R     | EGISTE | R |

# **Instruction Fields (Memory Shifts):**

dr field—Specifies the direction of the shift.

0 — Shift right

1 — Shift left

Effective Address field—Specifies the operand to be shifted. Only memory alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | _    | _              |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| – (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

# Bcc

# **Branch Conditionally**

Bcc

**Operation:** If Condition True

Then PC +  $d_n \rightarrow PC$

**Assembler**

Syntax: Bcc < label >

**Attributes:** Size = (Byte, Word)

**Description:** If the specified condition is true, program execution continues at location (PC) + displacement. The program counter contains the address of the instruction word for the Bcc instruction plus two. The displacement is a twos-complement integer that represents the relative distance in bytes from the current program counter to the destination program counter. If the 8-bit displacement field in the instruction word is zero, a 16-bit displacement (the word immediately following the instruction) is used.

Condition code cc specifies one of the following conditions:

| Mnemonic | Condition        |

|----------|------------------|

| CC(HI)   | Carry Clear      |

| CS(LO)   | Carry Set        |

| EQ       | Equal            |

| GE       | Greater or Equal |

| GT       | Greater Than     |

| HI       | High             |

| LE       | Less or Equal    |

| Mnemonic | Condition      |

|----------|----------------|

| LS       | Low or Same    |

| LT       | Less Than      |

| MI       | Minus          |

| NE       | Not Equal      |

| PL       | Plus           |

| VC       | Overflow Clear |

| VS       | Overflow Set   |

Condition Codes: Not affected.

### **Instruction Format:**

| 15 | 14                                               | 13 | 12 | 11        | 10 | 9 | 8                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|--------------------------------------------------|----|----|-----------|----|---|--------------------|---|---|---|---|---|---|---|---|

| 0  | 1                                                | 1  | 0  | CONDITION |    |   | 8-BIT DISPLACEMENT |   |   |   |   |   |   |   |   |

|    | 16-BIT DISPLACEMENT IF 8-BIT DISPLACEMENT = \$00 |    |    |           |    |   |                    |   |   |   |   |   |   |   |   |

#### **Instruction Fields:**

Condition field—The binary code for one of the conditions listed in the table.

- 8-Bit Displacement field—Twos complement integer specifying the number of bytes between the branch instruction and the next instruction to be executed if the condition is met.

- 16-Bit Displacement field—Used for the displacement when the 8-bit displacement field contains \$00.

### NOTE

A branch to the immediately following instruction automatically uses the 16-bit displacement format because the 8-bit displacement field contains \$00 (zero offset).

# **BCHG**

# **Test a Bit and Change**

**BCHG**

**Operation:** TEST ( < number > of Destination)  $\rightarrow$  Z;

TEST ( < number > of Destination)  $\rightarrow$  < bit number > of Destination

Assembler BCHG Dn, < ea >

Syntax: BCHG # < data > , < ea >

**Attributes:** Size = (Byte, Long)

**Description:** Tests a bit in the destination operand and sets the Z condition code appropriately, then inverts the specified bit in the destination. When the destination is a data register, any of the 32 bits can be specified by the modulo 32-bit number. When the destination is a memory location, the operation is a byte operation, and the bit number is modulo 8. In all cases, bit zero refers to the least significant bit. The bit number for this operation may be specified in either of two ways:

- 1. Immediate—The bit number is specified in a second word of the instruction.

- 2. Register—The specified data register contains the bit number.

### **Condition Codes:**

| X | N | Z | V | С |

|---|---|---|---|---|

| _ | _ | * | _ | _ |

X — Not affected.

N — Not affected.

Z — Set if the bit tested is zero; cleared otherwise.

V — Not affected.

C — Not affected.

# Instruction Format (Bit Number Dynamic, specified in a register):

|   | 15 | 14 | 13 | 12 | 11 | 10       | 9 | 8 | 7 | 6 | 5 | 4    | 3      | 2     | 1      | 0 |

|---|----|----|----|----|----|----------|---|---|---|---|---|------|--------|-------|--------|---|

| Γ | 0  | _  | _  | _  | _  | REGISTER | , | 4 | _ | 4 |   | EFF  | ECTIVE | ADDRE | SS     |   |

|   | U  | U  | U  | U  | r  | KEGISTER |   | ' | U | ı |   | MODE |        | R     | EGISTE | R |

# Instruction Fields (Bit Number Dynamic):

Register field—Specifies the data register that contains the bit number.

Effective Address field—Specifies the destination location. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn*                     | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Mode | Register |

|------|----------|

| 111  | 000      |

| 111  | 001      |

| _    | _        |

|      |          |

|      |          |

| _    | _        |

| _    | _        |

|      | 111      |

<sup>\*</sup>Long only; all others are byte only.

### Instruction Format (Bit Number Static, specified as immediate data):

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6          | 5 | 4   | 3      | 2     | 1  | 0      |   |

|----|----|----|----|----|----|---|---|---|------------|---|-----|--------|-------|----|--------|---|

| 0  | 0  | 0  | 0  | 1  | 0  | 0 | 0 | 0 | 1          |   | EFF | ECTIVE | ADDRE | SS |        |   |

| U  | 0  | 0  | "  | '  | 0  | 0 | 0 | " | '          | ' |     | MODE   |       | R  | EGISTE | R |

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |   | BIT NUMBER |   |     |        |       |    |        |   |

### **Instruction Fields (Bit Number Static):**

Effective Address field—Specifies the destination location. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn*                     | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| – (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

Bit Number field—Specifies the bit number.

<sup>\*</sup>Long only; all others are byte only.

# **BCLR**

### Test a Bit and Clear

**BCLR**

**Operation:** TEST ( < bit number > of Destination)  $\rightarrow$  Z;  $0 \rightarrow$  < bit number > of Des-

tination

Assembler BCLR Dn, < ea >

**Syntax:** BCLR # < data > , < ea >

**Attributes:** Size = (Byte, Long)

**Description:** Tests a bit in the destination operand and sets the Z condition code appropriately, then clears the specified bit in the destination. When a data register is the destination, any of the 32 bits can be specified by a modulo 32-bit number. When a memory location is the destination, the operation is a byte operation, and the bit number is modulo 8. In all cases, bit zero refers to the least significant bit. The bit number for this operation can be specified in either of two ways:

- 1. Immediate—The bit number is specified in a second word of the instruction.

- 2. Register—The specified data register contains the bit number.

### **Condition Codes:**

| Χ | N | Z | V | С |

|---|---|---|---|---|

| _ | _ | * | _ | _ |

X — Not affected.

N — Not affected.

Z — Set if the bit tested is zero; cleared otherwise.

V — Not affected.

C — Not affected.

# Instruction Format (Bit Number Dynamic, specified in a register):

| 15 | 14 | 13 | 12 | 11   | 10      | 9 | 8 | 7 | 6 | 5                 | 4    | 3 | 2 | 1      | 0 |

|----|----|----|----|------|---------|---|---|---|---|-------------------|------|---|---|--------|---|

| 0  | 0  | 0  | 0  | Ь    | EGISTER |   | 1 | 4 |   | EFFECTIVE ADDRESS |      |   |   |        |   |

|    | U  | U  | U  | , in | LGISTER |   | · | _ | 0 |                   | MODE |   | R | EGISTE | R |

# **Instruction Fields (Bit Number Dynamic):**

Register field—Specifies the data register that contains the bit number.

Effective Address field—Specifies the destination location. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn*                     | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

<sup>\*</sup>Long only; all others are byte only.

# **BCLR**

### **Test a Bit and Clear**

**BCLR**

### Instruction Format (Bit Number Static, specified as immediate data):

|   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7          | 6     | 5 | 4    | 3      | 2     | 1      | 0 |

|---|----|----|----|----|----|----|---|---|------------|-------|---|------|--------|-------|--------|---|

| ĺ | 0  | _  | _  | _  | 1  | _  | _ | _ | 1          | 0     |   | EFF  | ECTIVE | ADDRE | SS     |   |

|   | U  | "  | "  | "  | '  | "  | " | " | 1          | '   ' |   | MODE |        | R     | EGISTE | R |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | BIT NUMBER |       |   |      |        |       |        |   |

### **Instruction Fields (Bit Number Static):**

Effective Address field—Specifies the destination location. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn*                     | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

Bit Number field—Specifies the bit number.

<sup>\*</sup>Long only; all others are byte only.

**BRA**

# **Branch Always**

**BRA**

**Operation:**  $PC + d_n \rightarrow PC$

**Assembler**

Syntax: BRA < label >

**Attributes:** Size = (Byte, Word)

**Description:** Program execution continues at location (PC) + displacement. The program counter contains the address of the instruction word of the BRA instruction plus two. The displacement is a twos complement integer that represents the relative distance in bytes from the current program counter to the destination program counter. If the 8-bit displacement field in the instruction word is zero, a 16-bit displacement (the word immediately following the instruction) is used.

### **Condition Codes:**

Not affected.

### **Instruction Format:**

| 15 | 14                                               | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5   | 4        | 3     | 2  | 1 | 0 |

|----|--------------------------------------------------|----|----|----|----|---|---|---|---|-----|----------|-------|----|---|---|

| 0  | 1                                                | 1  | 0  | 0  | 0  | 0 | 0 |   |   | 8-B | IT DISPI | ACEME | NT |   |   |

|    | 16-BIT DISPLACEMENT IF 8-BIT DISPLACEMENT = \$00 |    |    |    |    |   |   |   |   |     |          |       |    |   |   |

#### Instruction Fields:

- 8-Bit Displacement field—Twos complement integer specifying the number of bytes between the branch instruction and the next instruction to be executed.

- 16-Bit Displacement field—Used for a larger displacement when the 8-bit displacement is equal to \$00.

#### **NOTE**

A branch to the immediately following instruction automatically uses the 16-bit displacement format because the 8-bit displacement field contains \$00 (zero offset).

BSET Test

# Test a Bit and Set BSET

**Operation:** TEST (< bit number > of Destination)  $\rightarrow$  Z; 1  $\rightarrow$  < bit number > of Des-

tination

Assembler BSET Dn, < ea >

Syntax: BSET # < data > , < ea >

**Attributes:** Size = (Byte, Long)

**Description:** Tests a bit in the destination operand and sets the Z condition code appropriately, then sets the specified bit in the destination operand. When a data register is the destination, any of the 32 bits can be specified by a modulo 32-bit number. When a memory location is the destination, the operation is a byte operation, and the bit number is modulo 8. In all cases, bit zero refers to the least significant bit. The bit number for this operation can be specified in either of two ways:

1. Immediate—The bit number is specified in the second word of the instruction.

2. Register—The specified data register contains the bit number.

### **Condition Codes:**

| Χ | Ν | Z | V | С |

|---|---|---|---|---|

| _ | _ | * | _ | _ |

X — Not affected.

N — Not affected.

Z — Set if the bit tested is zero; cleared otherwise.

V — Not affected.

C — Not affected.

# Instruction Format (Bit Number Dynamic, specified in a register):

| 15 | 14 | 13 | 12 | 11 | 10       | 9 | 8 | 7 | 6                 | 5 | 4    | 3 | 2 | 1      | 0 |

|----|----|----|----|----|----------|---|---|---|-------------------|---|------|---|---|--------|---|

|    | _  | _  | _  | _  | REGISTER |   |   |   | EFFECTIVE ADDRESS |   |      |   |   |        |   |

| 0  | 0  | U  | U  | K  | REGISTER |   | I | ı | ı                 |   | MODE |   | R | EGISTE | R |

### **Instruction Fields (Bit Number Dynamic):**

Register field—Specifies the data register that contains the bit number.

Effective Address field—Specifies the destination location. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn*                     | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| – (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

### Instruction Format (Bit Number Static, specified as immediate data):

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8          | 7 | 6 | 5 | 4    | 3      | 2     | 1       | 0 |

|----|----|----|----|----|----|---|------------|---|---|---|------|--------|-------|---------|---|

| 0  | _  | _  | 0  | 4  | _  | _ | 0          | 4 | 4 |   | EFF  | ECTIVE | ADDRE | ESS     |   |

| U  | 0  | 0  | U  | '  | 0  | 0 | U          | ' | ' |   | MODE |        | R     | REGISTE | R |

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | BIT NUMBER |   |   |   |      |        |       |         |   |

### **Instruction Fields (Bit Number Static):**

Effective Address field—Specifies the destination location. Only data alterable addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn*                     | 000  | reg. number:Dn |

| An                      | 1    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

Bit Number field—Specifies the bit number.

<sup>\*</sup>Long only; all others are byte only.

<sup>\*</sup>Long only; all others are byte only.

# **BSR**

### **Branch to Subroutine**

**BSR**

**Operation:** SP – 4  $\rightarrow$  SP; PC  $\rightarrow$  (SP); PC + d<sub>n</sub>  $\rightarrow$  PC

Assembler

Syntax: BSR < label >

**Attributes:** Size = (Byte, Word)

**Description:** Pushes the long-word address of the instruction immediately following the BSR instruction onto the system stack. The program counter contains the address of the instruction word plus two. Program execution then continues at location (PC) + displacement. The displacement is a twos complement integer that represents the relative distance in bytes from the current program counter to the destination program counter. If the 8-bit displacement field in the instruction word is zero, a 16-bit displacement (the word immediately following the instruction) is used.

### **Condition Codes:**

Not affected.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11  | 10       | 9      | 8      | 7         | 6      | 5      | 4        | 3      | 2  | 1 | 0 |

|----|----|----|----|-----|----------|--------|--------|-----------|--------|--------|----------|--------|----|---|---|

| 0  | 1  | 1  | 0  | 0   | 0        | 0      | 1      |           |        | 8-E    | BIT DISP | LACEME | NT |   |   |

|    | -  | -  | -  | 16- | BIT DISF | PLACEM | ENT IF | 8-BIT DIS | SPLACE | MENT = | \$00     |        |    |   |   |

### **Instruction Fields:**

8-Bit Displacement field—Twos complement integer specifying the number of bytes between the branch instruction and the next instruction to be executed.

16-Bit Displacement field—Used for a larger displacement when the 8-bit displacement is equal to \$00.

#### **NOTE**

A branch to the immediately following instruction automatically uses the 16-bit displacement format because the 8-bit displacement field contains \$00 (zero offset).

**Operation:** TEST (< bit number > of Destination)  $\rightarrow$  Z

Assembler BTST Dn, < ea >

**Syntax:** BTST # < data > , < ea >

**Attributes:** Size = (Byte, Long)

**Description:** Tests a bit in the destination operand and sets the Z condition code appropriately. When a data register is the destination, any of the 32 bits can be specified by a modulo 32- bit number. When a memory location is the destination, the operation is a byte operation, and the bit number is modulo 8. In all cases, bit zero refers to the least significant bit. The bit number for this operation can be specified in either of two ways:

- 1. Immediate—The bit number is specified in a second word of the instruction.

- 2. Register—The specified data register contains the bit number.

### **Condition Codes:**

| X | Ν | Z | V | С |

|---|---|---|---|---|

| _ | _ | * | _ | _ |

X — Not affected.

N — Not affected.

Z — Set if the bit tested is zero; cleared otherwise.

V — Not affected.

C — Not affected.

# Instruction Format (Bit Number Dynamic, specified in a register):

| 15 | 14 | 13 | 12 | 11 | 10       | 9 | 8 | 7 | 6 | 5                 | 4    | 3 | 2 | 1      | 0 |

|----|----|----|----|----|----------|---|---|---|---|-------------------|------|---|---|--------|---|

| 0  | 0  | 0  | 0  |    | REGISTER | ) | 1 | 0 |   | EFFECTIVE ADDRESS |      |   |   |        |   |

| U  | U  | O  | O  | r  | REGISTER | • | ' | U | U |                   | MODE |   | R | EGISTE | R |

### **Instruction Fields (Bit Number Dynamic):**

Register field—Specifies the data register that contains the bit number.

Effective Address field—Specifies the destination location. Only data addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn*                     | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | 111  | 100      |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | 111  | 010      |

| (d <sub>8</sub> ,PC,Xn) | 111  | 011      |

### Instruction Format (Bit Number Static, specified as immediate data):

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4      | 3      | 2     | 1      | 0 |

|----|----|----|----|----|----|---|---|---|---|---|--------|--------|-------|--------|---|

| 0  | 0  | 0  | 0  | -1 | 0  | 0 | 0 | 0 | 0 |   | EFF    | ECTIVE | ADDRE | ESS    |   |

| U  | "  | "  | 0  | '  | "  | " | " | " |   |   | MODE   |        | R     | EGISTE | R |

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |   |   |   | BIT NU | IMBER  |       |        |   |

### **Instruction Fields (Bit Number Static):**

Effective Address field—Specifies the destination location. Only data addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | 111  | 010      |

| (d <sub>8</sub> ,PC,Xn) | 111  | 011      |

Bit Number field—Specifies the bit number.

<sup>\*</sup>Long only; all others are byte only.

# CHK

# **Check Register Against Bounds**

**CHK**

**Operation:** If Dn < 0 or Dn > Source

Then TRAP

Assembler

Syntax: CHK < ea > ,Dn

**Attributes:** Size = (Word)

**Description:** Compares the value in the data register specified in the instruction to zero and to the upper bound (effective address operand). The upper bound is a twos complement integer. If the register value is less than zero or greater than the upper bound, a CHK instruction exception (vector number 6) occurs.

### **Condition Codes:**

| X | Ν | Z | V | С |

|---|---|---|---|---|

| _ | * | U | U | U |

X — Not affected.

N — Set if Dn < 0; cleared if Dn > effective address operand; undefined otherwise.

Z — Undefined.

V — Undefined.

C — Undefined.

### **Instruction Format:**

|   | 15 | 14 | 13 | 12 | 11 | 10       | 9 | 8   | 7          | 6 | 5                 | 4    | 3 | 2 | 1      | 0 |

|---|----|----|----|----|----|----------|---|-----|------------|---|-------------------|------|---|---|--------|---|

| ſ | 0  | 1  | 0  | 0  |    | REGISTER |   |     | CIZE       |   | EFFECTIVE ADDRESS |      |   |   |        |   |

|   | U  | !  | 0  | "  |    | REGISTER |   | 312 | <b>4</b> E |   |                   | MODE |   | R | EGISTE | R |

### **Instruction Fields:**

Register field—Specifies the data register that contains the value to be checked.

Size field—Specifies the size of the operation.

11 — Word operation

10— Long operation

Effective Address field—Specifies the upper bound operand. Only data addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| – (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | 111  | 100      |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | 111  | 010      |

| (d <sub>8</sub> ,PC,Xn) | 111  | 011      |

**CLR**

**Operation:**  $0 \rightarrow Destination$

**Assembler**

Syntax: CLR < ea >

Attributes: Size = (Byte, Word, Long)

**Description:** Clears the destination operand to zero. The size of the operation may be specified as byte, word, or long.

### **Condition Codes:**

| X | N | Z | V | С |  |  |

|---|---|---|---|---|--|--|

| _ | 0 | 1 | 0 | 0 |  |  |

X — Not affected.

N — Always cleared.

Z — Always set.

V — Always cleared.

C — Always cleared.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6  | 5 | 4    | 3       | 2     | 1      | 0 |

|----|----|----|----|----|----|---|---|-----|----|---|------|---------|-------|--------|---|

| 0  | 1  | 0  | _  | _  | 0  | 1 | _ | CI. | 7E |   | EFI  | FECTIVE | ADDRE | SS     |   |

| U  | '  | "  | "  | "  | "  | ' | " | 312 |    |   | MODE |         | R     | EGISTE | R |

### Instruction Fields:

Size field—Specifies the size of the operation.

00—Byte operation

01—Word operation

10—Long operation

Effective Address field—Specifies the destination location. Only data alterable addressing modes can be used as listed in the following table:

| <b>Addressing Mode</b>  | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An                      | _    | _              |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| – (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |

|-------------------------|------|----------|

| (xxx).W                 | 111  | 000      |

| (xxx).L                 | 111  | 001      |

| # <data></data>         | _    | _        |

|                         |      |          |

|                         |      |          |

| (d <sub>16</sub> ,PC)   | _    | _        |

| (d <sub>8</sub> ,PC,Xn) | _    | _        |

### **NOTE**

In the MC68000 and MC68008 a memory destination is read before it is cleared.

**Operation:** Destination – Source  $\rightarrow$  cc

**Assembler**

**Syntax:** CMP < ea > , Dn

**Attributes:** Size = (Byte, Word, Long)

**Description:** Subtracts the source operand from the destination data register and sets the condition codes according to the result; the data register is not changed. The size of the operation can be byte, word, or long.

### **Condition Codes:**

| Χ | Ν | Z | V | С |  |  |

|---|---|---|---|---|--|--|

| _ | * | * | * | * |  |  |

X — Not affected.

${\sf N}$  — Set if the result is negative; cleared otherwise.

Z — Set if the result is zero; cleared otherwise.

V — Set if an overflow occurs; cleared otherwise.

C — Set if a borrow occurs; cleared otherwise.

### **Instruction Format:**

| 15 | 14 | 13 | 12 | 11 | 10       | 9 | 8 | 7        | 6              | 5 | 4    | 3 | 2 | 1      | 0  |  |

|----|----|----|----|----|----------|---|---|----------|----------------|---|------|---|---|--------|----|--|

| 4  | 0  | 1  | 1  |    | REGISTER |   |   | ODMODE   | OPMODE EFFECTI |   |      |   |   | ADDRE  | SS |  |

| '  | 0  | '  | '  |    | CEGISTER |   | ` | JEIVIODE | -              |   | MODE |   | R | EGISTE | R  |  |

#### Instruction Fields:

Register field—Specifies the destination data register.

Opmode field

| Byte | Word | Long | Operation   |

|------|------|------|-------------|

| 000  | 001  | 010  | Dn - < ea > |

Effective Address field—Specifies the source operand. All addressing modes can be used as listed in the following table:

| Addressing Mode         | Mode | Register       |

|-------------------------|------|----------------|

| Dn                      | 000  | reg. number:Dn |

| An*                     | 001  | reg. number:An |

| (An)                    | 010  | reg. number:An |

| (An) +                  | 011  | reg. number:An |

| - (An)                  | 100  | reg. number:An |

| (d <sub>16</sub> ,An)   | 101  | reg. number:An |

| (d <sub>8</sub> ,An,Xn) | 110  | reg. number:An |

| Addressing Mode         | Mode | Register |  |  |

|-------------------------|------|----------|--|--|

| (xxx).W                 | 111  | 000      |  |  |

| (xxx).L                 | 111  | 001      |  |  |

| # <data></data>         | 111  | 100      |  |  |

|                         |      |          |  |  |

|                         |      |          |  |  |

| (d <sub>16</sub> ,PC)   | 111  | 010      |  |  |

| (d <sub>8</sub> ,PC,Xn) | 111  | 011      |  |  |

### **NOTE**

CMPA is used when the destination is an address register. CMPI is used when the source is immediate data. CMPM is used for memory-to-memory compares. Most assemblers automatically make the distinction.

<sup>\*</sup>Word and Long only.

# **CMPA**

# **Compare Address**

**CMPA**

**Operation:** Destination – Source  $\rightarrow$  cc

**Assembler**

Syntax: CMPA < ea > , An

Attributes: Size = (Word, Long)