# **Programming** 68000

**Steve Williams**

http://www.archive.org/details/programming6800000will

# Programming the 68000

# Programming the 62000

# Programming the 68000"

Steve Williams

Berkeley • Paris • Düsseldorf • London

Cover art by Judithe Sager Book design by Sharon Leong

CP/M is a registered trademark of Digital Research, Inc. CP/M-68K is a trademark of Digital Research. Motorola and UNIDOS are trademarks of Motorola, Inc. PDP-11 is a trademark of Digital Equipment Corporation. UNIX is a trademark of Bell Labs. SVBEX is not affiliated with any manufacturer.

Every effort has been made to supply complete and accurate information. However, SYBEX assumes no responsibility for its use, nor for any infringements of patents or other rights of third parties which would result.

Copyright© 1985 SYBEX Inc., 2344 Sixth Street, Berkeley, CA 94710. World rights reserved. No part of this publication may be stored in a retrieval system, transmitted, or reproduced in any way, including but not limited to photocopy, photograph, magnetic or other record, without the prior agreement and written permission of the publisher.

Library of Congress Card Number: ISBN 0-89599-133-0 Printed by Haddon Craftsmen Manufactured in the United States of America 10 9 8 7 6 5 4 3 2 1

# **Acknowledgments**

I would like to thank the following people who helped make this book possible: Mike McGrath of SYBEX for suggesting the book in the first place. My mother, Sylvia Williams, for providing that all-important "naive user" viewpoint. Steve Cliff for providing several important ideas for extensions to the book. Fran Borda, for her tireless effort in reviewing vast quantities of material in a very short time. Rod Coleman and Sage Computer Company for providing an affordable yet powerful 68000 machine. Mark of the Unicorn Software for providing the MINCE editor on CP/M-68K. Special thanks to Carole Alden and Scott Loewe, editors, and the SYBEX production staff for all their efforts and expertise: Valerie Robbins, word processing; Dawn Amsberry and Brenda Walker, proofreading; Sharon Leong, book design; Valerie Brewster and Janis Lund, typesetting.

# Contents

Introduction xviii

# **1** BASIC CONCEPTS

What Is Programming? 1

Algorithms 2 Programming Languages 2 Flowcharts 3

How Does a Computer Work? 5

1

Memory 5 Input/Output Devices 7 Central Processing Unit 7 CPU Organization 7 Stored Program Execution 9 Data Representation 11 What's in a K? 18 Extensions 24

Conclusion 24

Exercises 24

# 2 68000 ARCHITECTURE

### Introduction 29

Register Set 30 Address Registers 30 Data Registers 31 Program Counter 32 Status Register 32

# Data Organization in Memory 34

Bytes, Words, and Longwords 35 BCD 36 Floating Point 36 ASCII 37

# Addressing Modes 38

Effective Address 39 Data Register Direct Addressing 40 Address Register Direct Addressing 41 Address Register Indirect Addressing 43 Address Register Indirect Addressing with Post-increment 44 Address Register Indirect Addressing with Displacement 46 Address Register Indirect Addressing with Displacement 47 Address Register Indirect Addressing with Index 49 Absolute Short Addressing 51 Absolute Long Addressing 52 Program Counter with Displacement 54 Program Counter with Index 55 Immediate Mode 57 Status Register Addressing 58

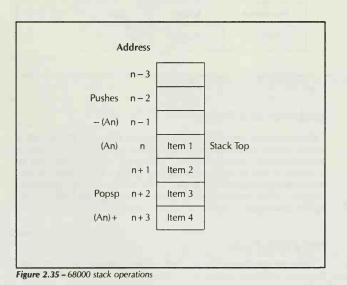

Stacks and Stack Frames 59 How a Stack Works 59 68000 Hardware Stack 60

Stack Implemented in Software 61 Stack Frames 62

Summary 62

Exercises 64

# **3** 68000 INSTRUCTION SET

# Introduction 67

# Instruction Classes 67

Data Movement 68 Integer Arithmetic Operations 68 Logical Operations 69 Shift and Rotate Operations 69 Bit Manipulation Operations 70 Binary Coded Decimal Instructions 70 Program Control Instructions 70 System Control Operations 71 67

# Program Development Mechanics 71

Editing 72 Backups 73 Assembling 73 Linking 74 Debugging 75 Example 76

## Instructions 80

Effective Address Operands 80 ABCD Instruction 81 ADD Instruction 84 ADDA Instruction 87 ADDI Instruction 89 ADDQ Instruction 91 ADDX Instruction 93 AND Instruction 95 **ANDI Instruction** 97 ASI Instruction 100 ASR Instruction 103 Bcc (Conditional Branch) Instruction **BCHG** Instruction 112 **BCLR Instruction** 114 **BSET Instruction** 116 **BSR** Instruction 118 **BTST Instruction** 120 CHK Instruction 123 **CLR** Instruction 125 CMP Instruction 127 CMPA Instruction 130 CMPI Instruction 132 **CMPM** Instruction 134 **DBcc** Instruction 136 **DIVS** Instruction 140 **DIVU Instruction** 142 FOR Instruction 144 EORI Instruction 146 **EXG** Instruction 148 EXT Instruction 150 ILLEGAL Instruction 152 **IMP** Instruction 153 **ISR** Instruction 155 LEA Instruction 157 LINK Instruction 159 LSL Instruction 162 LSR Instruction 164 MOVE Instruction 166 **MOVE to CCR Instruction** 168

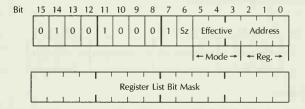

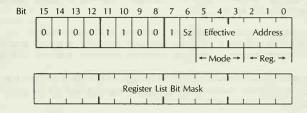

MOVE to SR Instruction 170 MOVE from SR Instruction MOVE USP Instruction 174 **MOVEA Instruction** 175 **MOVEM Instruction** 177 **MOVEP Instruction** 182 **MOVEQ** Instruction 185 **MULS** Instruction 187 MULU Instruction 189 NBCD Instruction 191 **NEG Instruction** 193 **NEGX** Instruction 195 NOP Instruction 197 NOT Instruction 198 **OR** Instruction 200 **ORI Instruction** 202 PEA Instruction 204 **RESET Instruction** 206 **ROL** Instruction 207 **ROR Instruction** 210 **ROXL Instruction** 213 **ROXR** Instruction 216 **RTE Instruction** 219 **RTR Instruction** 221 **RTS Instruction** 222 SBCD Instruction 223 Scc Instruction 226 **STOP Instruction** 229 SUB Instruction 230 SUBA Instruction 232 SUBI Instruction 234 SUBQ Instruction 236 SUBX Instruction 238 SWAP Instruction 240

TAS Instruction241TRAP Instruction243TRAPV Instruction244TST Instruction245UNLK Instruction247

Summary 248

Exercises 248

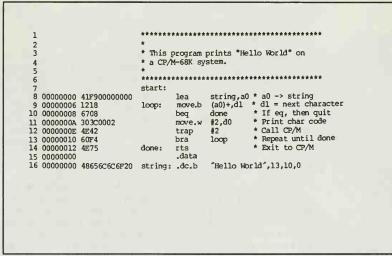

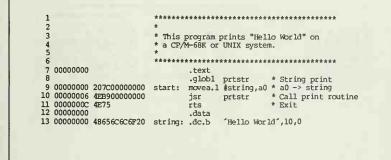

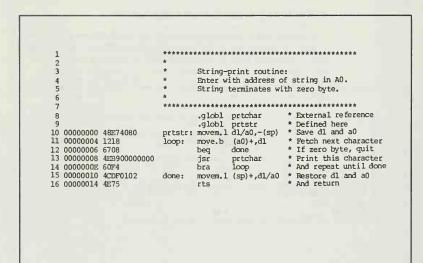

Introduction 251 Displaying a Line on the Terminal 251 Program Portability 254 Achieving Program Portability Across Operating Systems 254 A Portable String-Print Program 255 Conversion Routines 258 Binary to Hexadecimal Conversion 258 Binary to Decimal Conversion 260 Summing the First Five Integers 261 Reading Terminal Input 261 Input Conversion 265 Decimal to Hex Conversion 266 Summary 267 Exercises 268

Introduction 271 Types of I/O 271 Terminal I/O 272 File I/O 273 Character I/O 274 Special I/O 274

Device Independence 274

Interfacing to High-Level Languages 275

Interfacing to C 276

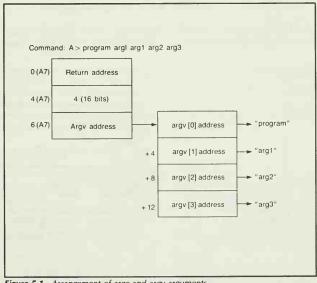

Calling Sequences 276 Two Arguments: Argc and Argv 278 Using Printf from Assembly Language 279

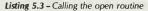

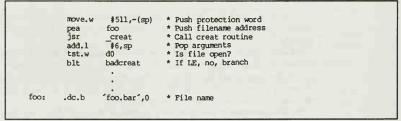

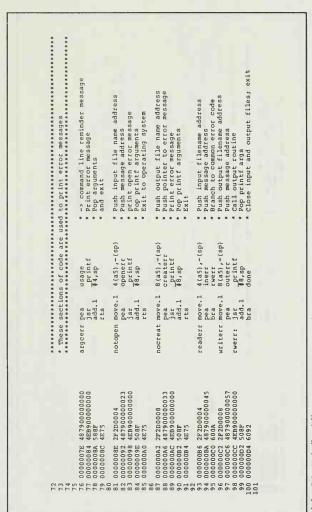

C Program I/O 279 Unbuffered I/O 280 Buffered I/O 285

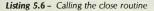

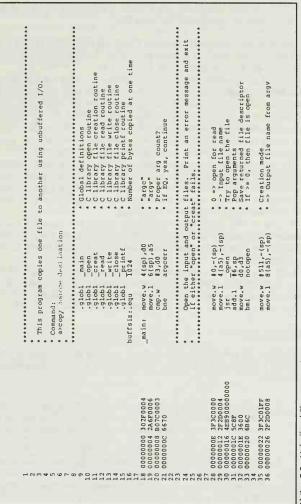

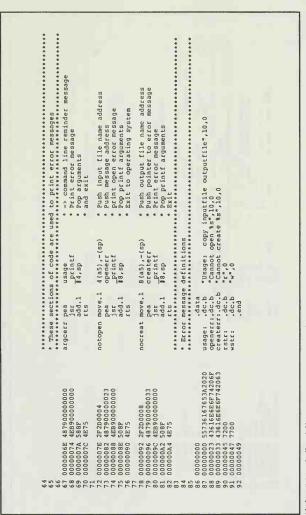

Buffered File Copy Program 297

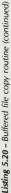

Standard I/O 297

Calling an Assembly Language Routine from C 301

Summary 303

Exercises 303

Introduction 305

Data Organization 305 Records 305 Describing Records in Assembly Language 305

Storage Allocation 308

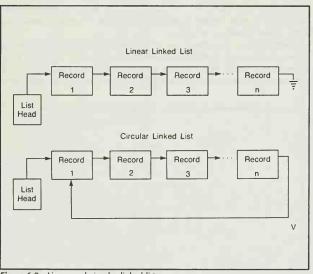

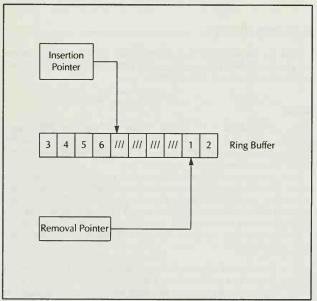

Arrays 308 Linked Lists 311

Data Structures 313

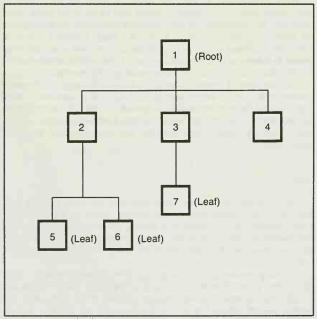

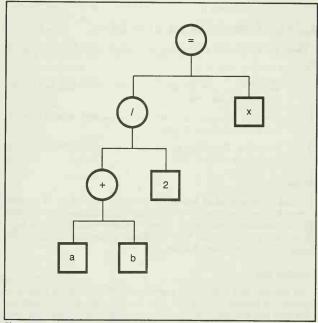

Stacks 313 Queues 314 Trees 315

Advanced Programming Concepts 318

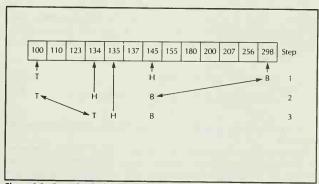

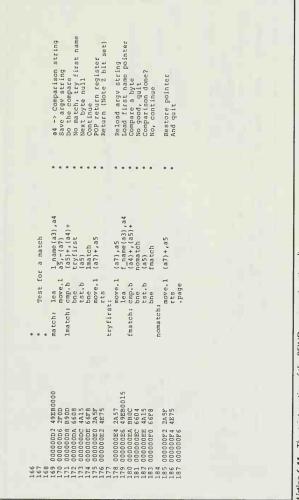

Sorting 318 Searching 320 Recursion 322

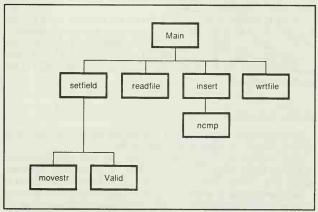

Sample Application System 323

PADD Program 324 PFIND Program 336 PLIST Program 345

Summary 345

Exercises 345

# **EXCEPTION PROCESSING**

Introduction 349

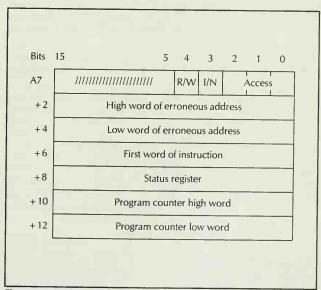

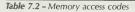

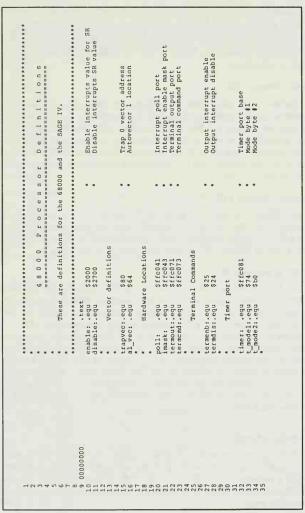

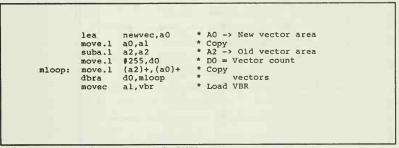

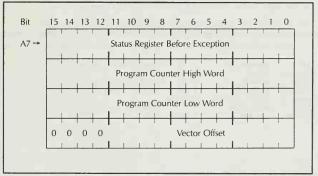

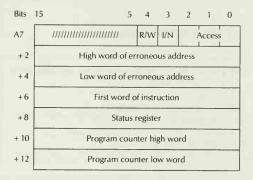

What Is an Exception? 349 General Exception Processing 350 Vectors 350 What Happens During an Exception? 352 RESET 352 BUSERR and Addressing Error Exceptions 352 Illegal Instruction Exceptions 355 TRAP Exceptions 355 Exceptions Used for Debuggers 356 Other Error Exceptions 357 Privilege Violation Exception 358 An Exception-Processing Program 358 Interrupts 365 Interrupt-Driven Serial Output 367

Sage IV Serial Output 367

Summary 371

Exercises 371

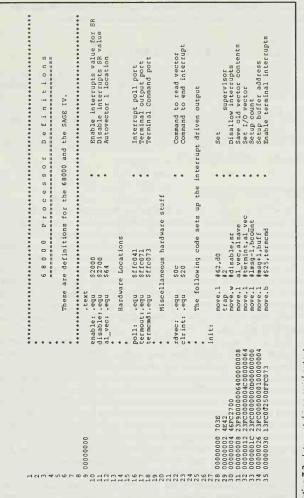

Introduction 375

# **8** CASE STUDY: A SAMPLE OPERATING SYSTEM 375

Operating System Concepts 375 Multitasking 376 Resource Management 377 Scheduling 378 Reentrant Coding379Mutual Exclusion379Deadlocks383

# Sample Operating System 383 System Services 383 Data Structures 385 Initialization Code 392 TRAP #0 Exception Handler 392

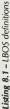

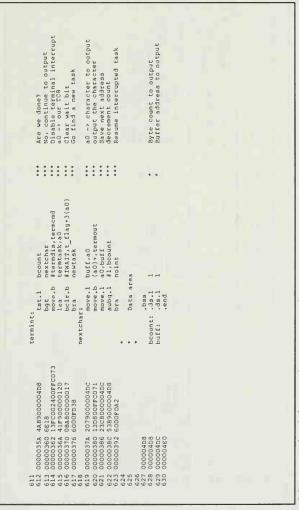

Newtask SVC and Dispatcher 392 Data Area 398 Interrupt Polling Routine 398 Send Message SVC 402 Receive Message SVC 402 Reply to Message SVC 406 Printline and Delay SVCs 406 Timer Task Code 406 Terminal Output Task 410 Application Tasks 410

Summary 410

Exercises 417

# **APPENDICES**

Chapter 1419Chapter 2426Chapter 3427Chapter 4427

| Chapter 5 | 431 |

|-----------|-----|

| Chapter 6 | 433 |

| Chapter 7 | 435 |

| Chapter 8 | 437 |

# **B** ASCII CHARACTER SET

# C PROGRAMMING STYLE

What Is a "Good" Program? 445

Programming Guidelines 446 Top-Down Program Design 446 Modular Programming 447 Top-Down Implementation and Testing 448 Coding Techniques 448 Program Documentation 451 Code Reviews 453

Conclusion 453

# **D** 68010

Introduction 457

Extra Registers in the 68010 457 Vector Base Register (VBR) 458 SFC and DFC Registers 458 441

445

Additional Instructions in the 68010 458

MOVE from CCR Instruction 460 MOVE Control Register Instruction 461 MOVE to/from Address Space 462 RTD Instruction 464

# Differences in the 68010 Exception Mechanism 465

Vector Base Register 465 Stack Format Differences 466

Loop Mode 470

E GLOSSARY

# **G** 68000 QUICK REFERENCE

Index 536

495

499

# Introduction

This book explains machine-language programming for the 68000 microprocessor family. The material is divided into three parts: an introduction to programming, an explanation of applications programming, and a discussion of systems programming. These three areas can be studied in succession or independently.

Chapter 1 provides an introduction to computer operation and programming for readers with no programming background. It covers basic hardware and software concepts. Experienced readers may wish to skim this material.

Chapters 2 through 6 provide the background necessary to write assembly-language appplication programs or subroutines, including the mechanics of generating programs and debugging them. These chapters also cover high-level languages and interfacing to operating systems. With this information, you will be able to write applications programs in assembly language. It may also be used for calling assembly-language routines from a high-level language program for efficiency or for access to lowlevel machine resources.

Chapters 7 through 8 are a lower level discussion of programming the 68000. These chapters deal with interrupts and other machine-level primitives. A small multitasking "operating system" is provided as a case study.

An important part of learning machine-language programming is picking up the jargon. Computer scientists have their own language. All terms in this book are explained as they occur. A glossary has also been provided as a study aid.

Computer programming is not difficult to learn. It does not require extreme mathematical proficiency or supernormal intelligence. It does, however, require diligence and, more importantly, practice. There is absolutely no substitute for sitting down at the machine and trying it for yourself. Type in the examples, try them out, make improvements, and above all, make mistakes. You will learn more from your errors than anything else.

# **Basic Concepts**

Machine-level computer programming has been called art, engineering, sorcery, and religion. It is all of these and more. Dealing with a computer at its own level can be a very rewarding (and frustrating) experience.

This book will introduce you to the joys and woes of this wondrous craft. We have attempted to minimize the mathematics involved; anyone who can add, subtract, multiply, and divide can make full use of all the material presented here.

This chapter will introduce you to the concepts on which modern computing is founded: algorithms, elementary hardware operations, and the binary and hexadecimal number schemes.

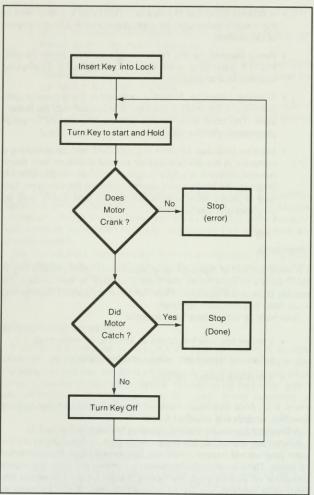

As a start toward learning how to program, consider the process of starting an automobile engine:

- 1. Insert the key into the lock.

- Turn the key past the ON position to the START position and hold.

- 3. If the motor does not crank, stop.

- 4. If the motor does catch, proceed to step 5. If the motor does not catch within 30 seconds, turn the key OFF and go to step 2.

- 5. Release the key back to the ON position, and stop.

This simple procedure has all of the same elements of a computer program:

- Step 1 is called an *initialization*. This is an action which is performed once at the start of a program.

- Steps 2 through 4 form a loop—a series of actions which is repeated until some condition is satisfied. (In this case, either the car starts or the battery expires.)

- Step 3 is an example of an error condition—some condition which causes the procedure to terminate in an abnormal fashion.

- Step 5 is the successful completion of the procedure.

# Algorithms

The above procedure, in computer terminology, is called an *algorithm*. Algorithms are stepwise procedures which can be used to define the steps in programs. Any step-by-step description is an algorithm. Some examples from everyday life are kitchen recipes and directions for getting from one place to another.

You can see from these examples that not all algorithms can be made into computer programs. Even if an algorithm is suitable for transforming into a program, it must first be put into a form the computer can recognize. Computers cannot utilize even the simplest English.

### **Programming Languages**

If you want a computer to carry out the steps you define in an algorithm, you must first translate the English description into a language that the computer can execute. Such a language is called a *programming language*. There are many such languages. The task to be performed generally dictates which language is to be used. Some examples of programming languages are:

- BASIC (Beginner's All-purpose Symbolic Instruction Code). BASIC is a very simple language to learn and to use. It is generally used for short, simple programs.

- COBOL (COmmon Business Oriented Language). COBOL is commonly used for business related software, such as payroll and other accounting applications.

- FORTRAN (FORmula TRANslation). FORTRAN is widely used in the scientific community for applications involving large numbers of calculations.

- Pascal (Named for the French mathematician Blaise Pascal).

Pascal is often used in universities to teach budding computer scientists how to program.

- Assembly Language. Assembly language is the process of programming a computer at the level of individual machine instructions. This book describes the process of assembly language programming for the 68000 computer.

- Machine Language. Machine language deals with programming a computer at the instruction level, without assistance from development software. Machine language involves using a numeric language: the binary codes directly usable by the computer. This type of programming is incredibly tedious, and is only used for very specialized applications.

### **Flowcharts**

A visual method of representing an algorithm is called *flowcharting*. A flowchart is a series of boxes which are connected by lines to show the possible paths of the algorithm. Flowcharting, like algorithm descriptions, is not done in a computer language.

Flowcharts consist of three basic symbols:

- a square box which indicates an action to be performed

- a diamond shaped box which indicates a decision

- · lines which connect the two.

There is an ANSI (American National Standards Institute) standard for flowchart symbols and flowchart layout.

A flowchart for our car-starting algorithm is shown in Figure 1.1.

A flowchart segment should fit on a single page. A flowchart for a computer program will require partitioning into several pages, interconnected by boxes. These boxes typically contain a number, indicating the mating connector on another page. Partitioning a large program flowchart into single-page segments is quite an involved process. It could require so much time that the exercise is not justified.

Figure 1.1 - Flowchart for car-starting algorithm

### **HOW DOES A COMPUTER WORK?**

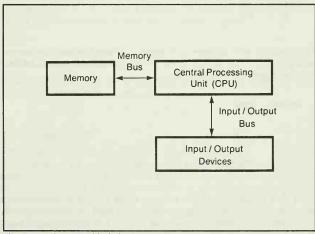

In order to learn programming, one must first understand how computer hardware functions. Figure 1.2 is a block diagram showing the major portions of a typical computer.

The memory contains the program which the computer follows, as well as the data on which the computer operates. In this simplified model of a computer, the box labeled central processing unit (CPU) is the "brains" behind the computer. The connection between the CPU and the computer's memory is known as the memory bus. Input/output (I/O) devices are the machines through which the computer interacts with the outside world. Examples of I/O devices are cathode ray tube (CRT) terminals (the computer's "TV screen"), floppy disk drives, and printers. The connection between the CPU and the I/O devices is called the input/ouput bus. Let us now examine each of these areas in detail.

### Memory

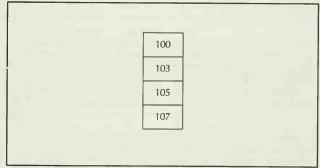

Computer memory is a series of numbered slots, called *locations*, each of which contains a number. The number of the location is called its

Figure 1.2 - Computer block diagram

address (like a street number). The number contained within the slot is called the *memory data* or *memory contents*. There are two operations associated with a computer memory:

- Change the contents of a location to a specific value. This operation is called a memory write or a memory store. The contents of the location before the write are lost.

- Obtain the present contents of a location. This operation is called a memory read or a memory fetch. A memory read does not alter the contents of the location—subsequent reads with no intervening writes will return the same value.

For example, suppose we have a four location memory with the following values:

| Address | Data |

|---------|------|

| 0       | 21   |

| 1       | 27   |

| 2       | 19   |

| 3       | 100  |

Note that memory addresses are always numbered sequentially, starting with zero. If we read location 2, we will get the result 19. Writing a 6 into location 1 gives the following values:

| Address | Data |

|---------|------|

| 0       | 21   |

| 1       | 6    |

| 2       | 19   |

| 3       | 100  |

Note that the memory write did not affect any other location. For example, reading location 2 again would again yield 19. Reading location 1 will yield 6. The original contents of location 1 (before the write) have been discarded, and may not be retrieved.

### Input/Output Devices

Input/output devices connect the computer to the outside world. These devices typically fall into one of two categories:

- Low-speed, character-oriented devices used to interact directly with people. Examples of this type of device are: CRT terminals, printers, and plotters.

- High-speed, block-oriented devices used for bulk storage of programs or data. Devices in this category such as disks, tapes, etc., are usually magnetic.

Character-oriented devices typically interact with human operators. This type of device usually transfers one character at a time. Many computer CRT terminals send and receive characters at 960 characters per second. Although this seems amazingly fast to a human sitting at a terminal, to a computer (which can handle millions of operations per second), it is extremely slow. When interacting with humans, the computer serond tremendous amount of time just waiting for characters from the terminal.

Block-oriented devices such as disks and tapes, on the other hand, do not normally interact with humans. These devices typically handle multicharacter blocks at a time, with a short interval between characters within a block, but a comparatively long interval between blocks.

### Central Processing Unit

The CPU is the heart of the computer. It executes the programs and manipulates the input/output devices.

### **CPU Organization**

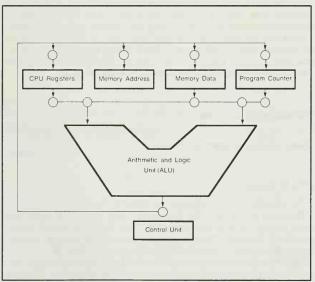

The organization of a typical CPU is shown in Figure 1.3.

The boxes on the top of the diagram are called registers. A register is a single memory location within the CPU which is used to store a temporary result. Different CPUs use different numbers and types of registers. The 68000 register set will be explained in detail in Chapter 2.

The CPU registers, which can be accessed much faster than main memory, are temporary memory locations used to facilitate program execution. There are usually a limited number of these registers. The memory address and memory data registers are used to access memory. For example, to read memory, the correct address is placed in the memory address register, and then the data can be read from the memory data register. To write to memory, the data is placed in the memory data register, and then the address is placed in the memory address register.

The program counter is a special register that is used to keep track of the next instruction to be executed. This process is detailed in the next section.

The Arithmetic and Logic Unit (ALU) performs all of the basic arithmetic operations, such as addition, subtraction, etc. The data on which the ALU operates can come from any of the registers with a path into the top of the ALU: the CPU registers, memory data, or the program counter. The result of the operation can be placed back into any of the registers.

Fortunately, programming the machine does not require attention to the inner operations of the ALU. The control unit supervises the movement of data through the ALU, and defines certain basic machine functions called *instructions*.

Figure 1.3 - CPU block diagram

### Stored Program Execution

The process of executing a program works like this:

- Fetch memory at the address indicated by the program counter, and increment the program counter to the next instruction in memory. The program counter is said to "point to" (i.e., contain the address of) the next instruction.

- 2. Perform the instruction.

- 3. Go back to step 1.

To illustrate how all this works together, we will now write a short program to add two numbers together. For simplicity, we will define a computer: Our simple computer has one register, named A. The machine can execute the following instructions:

| Instruction | Meaning                         |

|-------------|---------------------------------|

| 1nnn        | Copy memory location nnn into A |

| 2nnn        | Add memory location nnn to A    |

| 3nnn        | Copy A into memory location nnn |

| 4000        | Stop                            |

Now suppose that the computer memory contains the following:

| ocation | Contents | Instructions              |

|---------|----------|---------------------------|

| 100     | 1104     | Load location 104 into A  |

| 101     | 2105     | Add location 105 to A     |

| 102     | 3106     | Store A into location 106 |

| 103     | 4000     | Stop                      |

| 104     | 0300     | (Data)                    |

| 105     | 0400     | (Data)                    |

| 106     | 0000     | (Data)                    |

If we then set the program counter to 100 and cause the computer to execute, the program will execute as follows:

1. The contents of memory location 104 (300) will be copied into register A.

- 2. The contents of location 105 (400) will be added to register A. Register A will then contain 700.

- Register A will then be copied to memory location 106. This operation is called "Storing register A."

- 4. The machine will stop.

Upon completion of the above program, Register A and memory location 106 will have been altered to contain the value 700. This example is a program which adds two memory locations together and stores the result in a third memory location.

Programming at its most basic level is the process of putting the right instructions (also called operations or op codes) into the proper memory locations. The above program is an example of machine language programming, where the programmer deals with the actual numeric values of the instructions, and memory locations are assigned by hand. This is a tedious process at best, and programs called "assemblers" have been developed to handle the drudgery involved. Programming using an assembler is commonly called assembly language programming. The example program above, might look like this in assembly language:

|    | LOAD  | A,X |

|----|-------|-----|

|    | ADD   | A,Y |

|    | STORE | A,Z |

|    | STOP  |     |

| X: | DC    | 300 |

| Y: | DC    | 400 |

| z: | DC    | 0   |

The words LOAD, ADD, STORE and STOP are called *mnemonics*. A mnemonic is an alphabetical representation of a machine instruction. X, Y, and Z are called *labels*. A label is a way to tag a memory location without knowing what the final memory address will be. The assembler or another tool called the linker will make the final address assignment.

Finally, the abbreviation "DC" is an assembler directive. DC stands for "Define Constant." This directive tells the assembler to place a constant in memory at the location where the DC directive occurs.

Why is assembly language better than machine language? First, it is far more readable. Second, the task of changing an existing program is much simpler. Suppose that we wish to change our example program to add a third number, W, to X and Y. To add this to the assembly language version, we need add only two lines: an

ADD W,X

addition instruction, and a declaration for the new constant:

W: DC 50

To change the machine language version of the program, we must alter all of the instructions that reference memory, since the values to be added are now in a different place, as illustrated below:

| Location | Machine<br>Language | Assem | bly   | Language |

|----------|---------------------|-------|-------|----------|

| 100      | *1105               |       | LOAD  | A,X      |

| 101      | *2106               |       | ADD   | A,Y      |

| 102      | *2107               | *     | ADD   | A,W      |

| 103      | *3108               |       | STORE | A,Z      |

| 104      | 4000                |       | STOP  |          |

| 105      | 0300                | X:    | DC    | 300      |

| 106      | 0400                | Y:    | DC    | 400      |

| 107      | *0050               | *W:   | DC    | 50       |

| 108      | 0000                | Z:    | DC    | 0        |

|          |                     |       |       |          |

The asterisk character (\*) shows lines that have been changed. Note that no machine language location contains the same value as it did in the previous example. In large programs, altering machine code is a tremendous chore.

### **Data Representation**

The vast majority of computers represent numbers in a form involving only two possible values: ON and OFF. This is a property of the hardware used to implement the CPU, memory, and I/O devices. This two-value representation is called *binary*, or base 2.

### The Binary System

The binary system represents a number as a string of two-valued quantities. Each such quantity is called a *bit*, which stands for *Binary dig/T*. The ON and OFF values for a bit are 1 and 0, respectively. A bit with a value of 1 is said to be set; a bit with a value of 0 is said to be clear.

Most computers in use today organize bits in groups of eight to form a quantity known as a byte. The bits in a byte are numbered from right to left, starting at zero. Each bit is assigned a value twice the value of its neighbor on the right. Bit 0, the rightmost bit, has the value 1. The values associated with the eight bits in a byte are shown in Table 1.1.

| Bit<br>Number | Place<br>Value |

|---------------|----------------|

| 7             | 128            |

| 6             | 64             |

| 5             | 32             |

| 4             | 16             |

| 3             | 8              |

| 2             | 4              |

| 1             | 2              |

| 0             | 1              |

Table 1.1 - Binary Bit Values

Using this table of binary values, the binary number 0010 1111 has the value of 47. This is how the value for our example would be calculated.

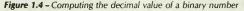

The decimal value of a binary number is equal to the bit number value times the place value, as shown in Figure 1.4.

The largest number that can be represented using eight bits is 1111 1111, which is decimal 255. It is the result of adding 128 + 64 + 32 + 16 + 8 + 4 + 2 + 1. For readability, we will write binary numbers as groups of four bits. In computerese, a four bit group, or one half of a byte, is called a *nibble*.

To represent numbers bigger than 255, two or more bytes are used. Common combinations are two bytes (16 bits), and four bytes (32 bits). These quantities are called a *word* and a *longword*, respectively. Dealing with 16 and 32 digit numbers can be cumbersome, however, so an abbreviated form of binary representation called *hexadecimal* (or base 16) is often used.

### **Hexadecimal Numbers**

In hexadecimal (hex) representation, a nibble is encoded as one hexadecimal digit.

These digits have values from 0 to 15. The values for 10 through 15 are represented by the letters A through F. Each digit in a hex number has a place value of sixteen times the value of its neighbor to the right. For instance, the number 22 hex is  $(2 \times 16) + 2$ , or 34.

### **Converting Binary to Hex**

A hex number can be derived from a binary number by first grouping the binary number into groups of four bits (nibbles), and then computing

| Bit Numbe<br>Bit Value | r 765<br>001    |       |                |   |                  |

|------------------------|-----------------|-------|----------------|---|------------------|

| Bit<br>Number          | Binary<br>Value |       | Place<br>Value | = | Decimal<br>Value |

| 7                      | 0               | ×     | 128            | - | 0                |

| 6                      | 0               | ×     | 64             | - | 0                |

| 5                      | 1               | ×     | 32             | = | 32               |

| 4                      | 0               | ×     | 16             | - | 0                |

| 3                      | 1               | ×     | 8              | - | 8                |

| 2                      | 1               | ×     | 4              | - | 4                |

| 1                      | 1               | ×     | 2              | - | 2                |

| 0                      | 1               | ×     | 1              | - | 1                |

| Converted              | decimal         | value |                | = | 47               |

the proper hex digit for each group using the 8-4-2-1 values for the bits in the group. For example, the number 0010 1111 in binary is 2F in hex:

8421

$0010 = (0 \times 8) + (0 \times 4) + (1 \times 2) + (0 \times 1) = 2$ 1111 = (1 × 8) + (1 × 4) + (1 × 2) + (1 × 1) = F (15)

### **Converting Hex to Binary**

Hex numbers can be converted to binary by first taking each hex digit and then expanding it into four binary bits using the hex, decimal, and binary values shown in Table 1.2.

| Hex Value | Decimal Value | Binary Value |

|-----------|---------------|--------------|

| 0         | 0             | 0000         |

| 1         | 1             | 0001         |

| 2         | 2             | 0010         |

| 3         | 3             | 0011         |

| 4         | 4             | 0100         |

| 5         | 5             | 0101         |

| 6         | 6             | 0110         |

| 7         | 7             | 0111         |

| 8         | 8             | 1000         |

| 9         | 9             | 1001         |

| А         | 10            | 1010         |

| В         | 11            | 1011         |

| С         | 12            | 1100         |

| D         | 13            | 1101         |

| E         | 14            | 1110         |

| F         | 15            | 1111         |

Table 1.2 - Hex, Decimal, and Binary Values

When you use this table, the hex number 2F converts to the binary number 0010 1111.

#### **Converting Hex to Decimal**

To convert a hex number to a decimal number, first multiply each digit by its appropriate place value, and then add the resulting numbers. The place values for hex numbers are shown in Table 1.3.

| Digit | Place<br>Value |

|-------|----------------|

| 0     | 1              |

| 1     | 16             |

| 2     | 256            |

| 3     | 4,096          |

| 4     | 65,536         |

| 5     | 1,048,576      |

| 6     | 16,777,216     |

| 7     | 268,435,456    |

Table 1.3 - Hexadecimal Place Values

The digit numbered 0 is the rightmost digit in a hex number. Each place value is derived by multiplying the previous place value by 16, starting with a value of 1 for the rightmost digit. The digit number is also known as a "power of 16."

The hex number 54321 converts to its decimal value as shown in Figure 1.5, the hex number A25 converts to its decimal value as shown in Figure 1.6, and the hex number 1234 converts to the decimal value of 4660 as shown in Figure 1.7.

|      | Digit     | ×    | Place<br>Value | = | Decimal<br>Value |

|------|-----------|------|----------------|---|------------------|

|      | 5         | ×    | 65,536         |   | 327,680          |

|      | 4         | ×    | 4,096          | = | 16,384           |

|      | 3         | ×    | 256            | - | 768              |

|      | 2         | ×    | 16             | - | 32               |

|      | 1         | ×    | 1              | - | + 1              |

| Conv | verted de | cima | l value        | - | 344,865          |

Figure 1.5 - Converting the hex number 54321 to its decimal value

| Di | ex :<br>igit |   | Place<br>Value | - | Deci<br>Val |       |

|----|--------------|---|----------------|---|-------------|-------|

| A  | (10)         | × | 256            |   |             | 2,560 |

|    | 2 :          | × | 16             |   |             | 32    |

|    | 5 :          | × | 1              |   | +           | 5     |

Figure 1.6 - Converting the hex number A25 to its decimal value

| Hex<br>Digit   | Place<br>Value                 | Decimal<br>Value |  |  |  |  |  |

|----------------|--------------------------------|------------------|--|--|--|--|--|

| 1              | 4096                           | 4096             |  |  |  |  |  |

| 2              | 256                            | 512              |  |  |  |  |  |

| 3              | 16                             | 48               |  |  |  |  |  |

| 4              | 1                              | + 4              |  |  |  |  |  |

| Converted deci | Converted decimal value = 4660 |                  |  |  |  |  |  |

Figure 1.7 - Converting the hex number 1234 to its decimal value

#### **Converting Decimal to Hex**

Decimal numbers can be converted to hex numbers using the inverse of the above technique. To convert a decimal number to hex, first find the largest place value in Table 1.3 that divides into the number to be converted, then divide the decimal value by this number. The quotient of this division is the hex digit. Divide the remainder by the next smallest place value to obtain the next hex digit (even if it's zero). Divide this remainder by the next smallest place value, to get the next digit and so on.

To convert the decimal number 123,456 to hex, we start with a hex place value of 65,536 and divide this hex value into the decimal value of 123,456. The result of 1 is the first hex digit and the remainder (57,920) is the dividend for the next hex place value.

| Decimal<br>Remaine |     | ÷ | Hex<br>Place<br>Value | = | Hex<br>Digit   |

|--------------------|-----|---|-----------------------|---|----------------|

| 123,4              | 456 | ÷ | 65,536                | - | 1              |

| 57,9               | 920 | + | 4,096                 | - | E (14 decimal) |

| 5                  | 576 | ÷ | 256                   | - | 2              |

|                    | 64  | + | 16                    | = | 4              |

|                    | 0   | ÷ | 1                     | - | 0              |

Read the answer down the Hex Digit column: 1E240. The next remainder can be calculated on a decimal calculator as: Present decimal remainder – (place value  $\times$  hex digit).

For example, the remainder 576 was calculated above by first dividing 4,096 into 57,920. The answer is 14, or a hex value of E. Then the hex place value was multiplied by 14, which equals 57,344. Finally, the remainder of 576 was arrived at by subtracting 57,344 from the previous remainder, 57,920.

There are several calculators on the market which will do hex and decimal conversions. If you are going to be writing a lot of machine code, a hex calculator will pay for itself in short order.

## What's in a K?

The hex number 800 translates to 1,024 in decimal. The term K (for "Kilo") is used in computer terminology to represent multiples of 1,024. Memory and disk device capacities are expressed in units of kilobytes. For

instance, a 64 kilobyte (64K) memory contains  $64 \times 1,024$ , or 65,536 decimal (or 10000 hex) bytes of memory.

Similarly, the number 100000 hex (1,048,576 decimal) is the result of multiplying  $1024 \times 1024$ . This number is commonly abbreviated *M* (for Mega). Megabyte units are used to describe the capacities of larger memory and disk devices. A 5-megabyte (commonly written 5Mb) disk therefore contains  $5 \times 1,048,576$ , or 5,242,880 bytes.

#### **Operations on Binary Numbers**

Since decimal, binary, and hex are simply alternate ways of representing numbers, the same operations that can be performed on decimal numbers can also be performed on binary or hex numbers. One can apply techniques similar to those used for decimal numbers for the addition, subtraction, multiplication, and division of hex and binary numbers. For programming, however, it is important to understand the operations a computer is capable of performing.

A computer's ALU is capable of performing a number of very simple operations on binary numbers. These include: One's complement, AND, OR, Exclusive OR, addition, two's complement, shifts and rotates. We will now explore these in greater detail.

#### **One's Complement**

One of the simpler operations on binary numbers is to take the one's complement: Simply invert the values of all the bits. All 0's become 1's and vice versa.

For example, complementing the number 0011 1100 (3C hex) produces 1100 0011 (C3 hex). Complementing 0000 0000 (00 hex) yields 1111 1111 (FF hex). Complementing the complement of a number yields the original number again.

#### **Binary AND**

Performing an AND operation on two binary numbers produces a third binary number with 1's in each bit position where the original numbers both had a 1. ANDing 0000 1101 (0D hex) with 1001 1001 (99 hex) yields 0000 1001 (09 hex).

The AND operation is commonly used to obtain a remainder for a division by a power of two (2, 4, 8, 16, etc.). To obtain such a remainder, AND the number with the power of 2 minus 1. For example, to find the remainder when 0011 1101 (3D hex) is divided by 8, AND with 0000 0111 (07 hex). The result is 0000 0101 (05 hex). 3D hex is  $3 \times 16 + 13$ , or 61 decimal. Dividing by 8 yields 7, with a remainder of 5.

#### **Binary OR**

The OR operation takes two binary numbers and produces a third binary number that has a 1 where either of the original numbers had a 1. For example, ORing 1010 1010 (AA hex) with 0101 0101 (55 hex) yields 1111 1111 (FF hex). (ANDing these two numbers gives all zeros.)

#### **Binary XOR**

The XOR (eXclusive OR) operation takes two binary numbers and produces a third binary number which has 1's in bit positions where one (not both) of the original numbers had a 1. For example, XORing 0101 0101 (55 hex) with 1111 1111 (FF hex) yields 1010 1010 (AA hex). XORing a number with all 1's yields the 1's complement of the number. XORing a number with itself produces zero.

#### **Binary Addition**

Adding two binary numbers is similar to adding decimal numbers. You add each pair of digits, starting on the right, and carry any result over 1 to the next column. For example, adding 0011 1101 (3D hex) and 0001 0101 (15 hex) is done as follows:

| Carry | 0011<br>0011<br>+ 0001 | 1010<br>1101<br>0101 | (3D hex)<br>(15 hex) |

|-------|------------------------|----------------------|----------------------|

| Sum   | 0101                   | 0010                 | (52 hex)             |

This procedure can be used for binary numbers of any length.

#### 2's Complement Arithmetic

Subtraction involves a bit of magic. Negative numbers are stored in a form known as two's complement. The two's complement of a number is

obtained by taking the one's complement (as explained above), and adding 1 to it. For instance, the two's complement of 0000 0001 is:

| Original Number:              | 0000           | 0001         | (01 hex)             |

|-------------------------------|----------------|--------------|----------------------|

| One's Complement:<br>Add One: | 1111<br>+ 0000 | 1110<br>0001 | (FE hex)<br>(01 hex) |

| Two's Complement:             | 1111           | 1111         | (FF hex)             |

Adding the two's complement of a number is the same as subtracting the number. As an example, consider adding 1111 1111 (FF hex) to 0000 0010 (02 hex). The leftmost bit of a two's complement number will be a 0 if the number is positive (zero or greater), and a 1 if the number is negative (less than 0). For this reason, the leftmost bit is often called the *sign bit*.

| Sum   | 0000   | 0001 | (01 hex) |

|-------|--------|------|----------|

|       | + 1111 | 1111 | (FF hex) |

|       | 0000   | 0010 | (02 hex) |

| Carry | 11111  | 1100 |          |

Note that the carry out of the high order bit position is discarded. This is due to the fact that all of the numbers kept in a computer have exactly the same number of bits (eight in this example). Note that the result of adding 02 hex and FF hex is 01. This is the same as subtracting 1 from 2. FF hex is the two's complement of 01 hex, as shown above.

Two's complement changes the range of numbers it is possible to represent using a given number of bits. For instance, without using the two's complement, we could represent from 0 to 255 with eight bits. Using two's complement, however, we can represent from -128 to +127.

The first case is called *unsigned* arithmetic, meaning that only positive numbers can be represented. The second case is called two's complement representation, meaning that both positive and negative numbers can be represented.

#### **Shifts and Rotates**

Two other operations commonly performed on binary numbers are shifts and rotates. These operations are similar to the old "bucket brigade" operation used in fighting fires. Bits are moved from one position to the next position. Shifts and rotates can occur in either direction.

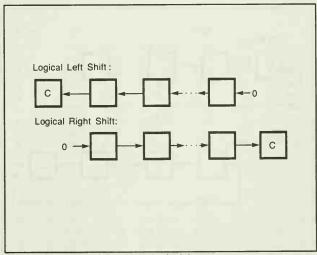

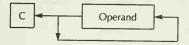

There are two types of shifts: logical and arithmetic. In a logical shift operation, the bits are moved left or right as in Figure 1.8.

Zero bits are shifted into the bit vacated by the shift operation. The bit marked C is a special status bit in one of the CPU internal registers. This bit is called the *Carry* bit, and it receives the bit which would otherwise be lost.

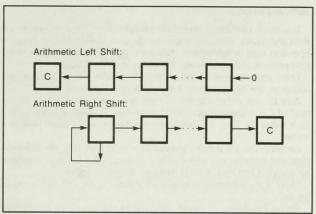

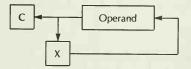

An arithmetic left shift is the same as a logical left shift. An arithmetic right shift is similar to a logical right shift, except that the most significant bit is copied into itself. Both of these are shown in Figure 1.9.

There is no difference between an arithmetic left shift and a logical left shift.

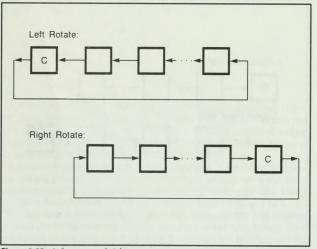

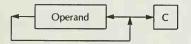

Rotates are similar to logical shifts, except that the Carry bit is shifted into the vacated bit, instead of a zero, as illustrated in Figure 1.10.

Figure 1.8 - Logical left shift and logical right shift

Figure 1.9 - Arithmetic left shift and arithmetic right shift

Figure 1.10 - Left rotate and right rotate

## Examples

The following examples assume that the Carry bit is initially zero. The original number is 1010 1010 (AA hex).

## Logical Shifts:

| Times | Left |      |          | Right |      |          |

|-------|------|------|----------|-------|------|----------|

| 0     | 1010 | 1010 | (AA hex) | 1010  | 1010 | (AA hex) |

| 1     | 0101 | 0100 | (54 hex) | 0101  | 0101 | (55 hex) |

| 2     | 1010 | 1000 | (A8 hex) | 0010  | 1010 | (2A hex) |

| 3     | 0101 | 0000 | (50 hex) | 0001  | 0101 | (15 hex) |

| 4     | 1010 | 0000 | (A0 hex) | 0000  | 1010 | (0A hex) |

| 5     | 0100 | 0000 | (40 hex) | 0000  | 0101 | (05 hex) |

| 6     | 1000 | 0000 | (80 hex) | 0000  | 0010 | (02 hex) |

| 7     | 0000 | 0000 | (00 hex) | 0000  | 0001 | (01 hex) |

| 8     | 0000 | 0000 | (00 hex) | 0000  | 0000 | (00 hex) |

|       |      |      |          |       |      |          |

Arithmetic shifts:

| Times | Left |      |          | Right |      |          |

|-------|------|------|----------|-------|------|----------|

| 0     | 1010 | 1010 | (AA hex) | 1010  | 1010 | (AA hex) |

| 1     | 0101 | 0100 | (54 hex) | 1101  | 0101 | (D5 hex) |

| 2     | 1010 | 1000 | (A8 hex) | 1110  | 1010 | (EA hex) |

| 3     | 0101 | 0000 | (50 hex) | 1111  | 0101 | (F5 hex) |

| 4     | 1010 | 0000 | (A0 hex) | 1111  | 1010 | (FA hex) |

| 5     | 0100 | 0000 | (40 hex) | 1111  | 1101 | (FD hex) |

| 6     | 1000 | 0000 | (80 hex) | 1111  | 1110 | (FE hex) |

| 7     | 0000 | 0000 | (00 hex) | 1111  | 1111 | (FF hex) |

| 8     | 0000 | 0000 | (00 hex) | 1111  | 1111 | (FF hex) |

Rotates:

| Time | es C Left |      |          | Right |      | C          |

|------|-----------|------|----------|-------|------|------------|

| 0    | 0 1010    | 1010 | (AA hex) | 1010  | 1010 | (AA hex) 0 |

| 1    | 1 0101    | 0100 | (54 hex) | 0101  | 0101 | (55 hex) 0 |

| 2    | 0 1010    | 1001 | (A9 hex) | 0010  | 1010 | (2A hex) 1 |

| 3    | 1 0101    | 0010 | (52 hex) | 1001  | 0101 | (95 hex) 0 |

| Time | es C | Left |      |          | Right |      | С          |

|------|------|------|------|----------|-------|------|------------|

| 4    | 0    | 1010 | 0101 | (A5 hex) | 0100  | 1010 | (4A hex) 1 |

| 5    | 1    | 0100 | 1010 | (4A hex) | 1010  | 0101 | (A5 hex) 0 |

| 6    | 0    | 1001 | 0101 | (95 hex) | 0101  | 0010 | (52 hex) 1 |

| 7    | 1    | 0010 | 1010 | (2A hex) | 1010  | 1001 | (A9 hex) 0 |

| 8    | 0    | 0101 | 0101 | (55 hex) | 0101  | 0100 | (54 hex) 1 |

| 9    | 0    | 1010 | 1010 | (AA hex) | 1010  | 1010 | (AA hex) 0 |

Shifts are very useful for multiplying and dividing. A logical shift left is the same as multiplying a number by 2, and a logical shift right is the same as dividing a number by 2. This is only true for unsigned numbers.

Arithmetic shifts, on the other hand, represent multiplication and division by 2 for two's complement numbers. The one exception is that dividing (shifting right) -1 yields -1 and not zero.

#### Extensions

When copying an 8-bit quantity into a 16-bit quantity, or when copying a 16-bit quantity into a 32-bit quantity, there is a possibility of losing the two's complement properties of the number.

To illustrate the problem, suppose we copy FF hex (-1 as an 8-bit number) to a 16-bit number. Copying only the lower 8 bits gives us 00FF hex, which is not -1, but 255! The way to fix this situation is to copy the sign bit (most significant bit) into all the "extra" bits in the larger number. This is called *sign* extension. If we sign extend FF hex into 16 bits, we get FFFF hex, which is -1 in two's complement form.

## Conclusion

In this chapter we have learned basic concepts that are applicable to most computers on the market today. In the next chapters, we shall see how these concepts are applied to a specific type of computer, the Motorola 68000.

## Exercises

Use the following questions to help solidify your understanding of the material presented in Chapter 1. Answers to all exercise question can be found in Appendix A.

- 1. Write an algorithm for converting a decimal number to hex.

- 2. Develop a flowchart for the algorithm in question 1.

- 3. Suppose the computer on page 9 has an additional instruction 5nnn, which subtracts the contents of memory location nnn from Register A. The assembly form of this instruction is SUB A,y where y is a label on the memory location to be subtracted from A. Modify the example of the machine-language program to compute the difference between the contents of location 105 and the contents of location 104. Store the result in location 106. (Hint: You will have to load location 105 into Register A first. Why?)

- 4. Move the machine-language program you wrote in question 3 to run at address 200.

- Give the assembly language equivalent of the program for question 3.

- 6. Write a new assembly language program that computes the sum of the first five integers. Use the labels A through E for the memory locations that contain the numbers to be added. Store the result in a separate memory location, labeled F.

- Convert the following decimal numbers to their hex and binary equivalents.

- 273 421 1024 100

- 8. Convert the following hex numbers to their binary and decimal equivalents.

- 9. Give the one's and two's complements for each of the numbers in the previous question.

- 10. Perform the AND, OR, XOR, and addition operations on the following pairs of hex numbers. Use 16-bit operations. Give the carry out of the high order bit pairs for the addition operation.

A5A5 5A5A FFFF 0001 1234 4321

Prepare shift and rotate tables similar to those in the text for the hex quantities FF and 55. Assume that the carry bit is initially zero.

# 68000 Architecture

# INTRODUCTION

In this chapter, we will expand the general programming concepts presented in Chapter 1 to cover the architecture of the Motorola 68000. The information specific to the 68000 is necessary in order to understand the instruction set contained in Chapter 3.

Most computers can be categorized by the following criteria:

- The number and type of registers that may be used by the programmer in writing software.

- How data is organized in memory, and what data types are supported with hardware instructions.

- · How memory is addressed by an instruction.

- Special hardware features, such as hardware support for stacks.

We will now explore each of these areas as it relates to the 68000.

## **REGISTER SET**

One of the first questions you should ask when learning a new computer is "How many registers does it have?" Another important consideration is whether the registers can be used interchangeably or not. If the computer has many registers that can be used interchangeably, you will have a great deal of flexibility in handling intermediate values in a computation.

The number of registers in a computer also has an effect on program speed and size. Computations using a register are usually smaller and faster than computations involving a memory location. (This is due primarily to the nature of computer hardware). A machine with a large number of general-purpose registers is preferred over a machine with a small number of registers or a machine whose registers are restricted in function.

The 68000 architecture trades off some generality in order to gain a larger register set. There are two types of registers: address registers and data registers. Address registers are normally used to contain memory addresses, while data registers normally contain data. The two register classes are not used interchangeably.

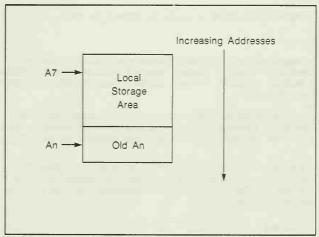

## **Address Registers**

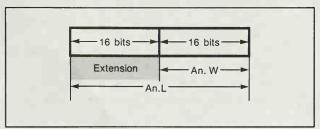

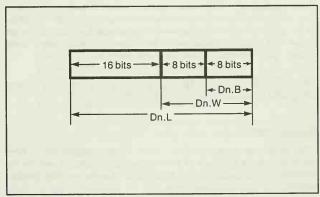

There are eight address registers, numbered A0–A7. Each address register is a 32-bit quantity. Address registers can also be used as 16-bit quantities. When a 16-bit quantity is loaded into an address register, it is sign extended to become a 32-bit quantity, as shown in Figure 2.1. The notation A0.W is used to mean the word part of address register A0. (A0.L means the entire 32 bits stored in register A0.) The .B suffix is used to denote an 8-bit quantity. Address registers may not be used as 8-bit quantities, however.

Figure 2.1 - Address register layout

Register A7 is a special-purpose register. A7 is the hardware stack pointer used by 68000 exceptions and subroutine call instructions. This register is also used by programs for temporary storage of data. The concept of a stack is discussed later in this chapter.

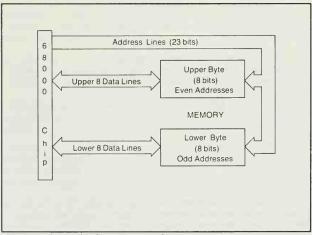

Address registers are used as temporary locations for storing memory addresses. These registers can be used in instructions that reference memory in order to specify the address at which data is located. The upper byte of the register is presently ignored in such usage (by the 68000 and 68010 chips). This limits the amount of memory that you can use to 16 megabytes (16,772,216 bytes). Future processors in the 68000 family will not ignore this byte, so it should always be set to zero for compatibility.

#### **Data Registers**

The 68000 also has eight other registers, called *data registers*, numbered D0–D7. A data register can be used as an 8-bit, 16-bit, or 32-bit quantity, as shown in Figure 2.2. Unlike address registers, loading a data register with less than 32 bits does not cause a sign extension to occur into the remaining bits in the register. These remaining bits are left unchanged.

Data registers cannot be used to address memory in an instruction. These registers are used instead as temporary locations where data may be stored. Many instructions require one or more of the operands to reside in a data register.

Figure 2.2 - Data register layout

#### **Program Counter**

A special 32-bit register called the program counter is used to control execution of the program in memory. The program counter always contains the memory address of the next instruction to be executed. As an instruction is executed, the program counter is advanced to point to the next instruction.

Certain instructions can be used to affect the contents of the program counter. These are:

- Instructions that alter the contents of the program counter unconditionally. These are called unconditional branches or jumps. Such an instruction is useful for programming loops, or for merging several alternative sections of the program into one common section.

- Instructions that alter the contents of the program counter based on the result of a previous instruction. These are called conditional branches, and enable the computer to make decisions. Using a conditional branch, either a portion of the program can be skipped or a previous portion repeated, based on the result of a previous computation.

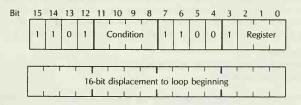

- Instructions that cause a given section of code to be repeated a specific number of times, or until a condition is satisfied. Such instructions are called *looping primitives*.

- Instructions that are used to branch to another area of the program and then to return to the location following the original branch. This technique is known as a *subroutine* call. A subroutine call can be used to invoke a common function, such as an I/O routine, at many points in the program, using only a single copy of the instructions that perform the I/O.

As with address registers, the upper eight bits of the program counter are ignored by the 68000 and 68010 processors.

## **Status Register**

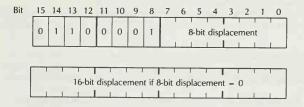

The 68000 uses a special register, called the status register (SR) to store information about the status of the machine. This register is used by the conditional branch instructions to retrieve information about the last instruction.

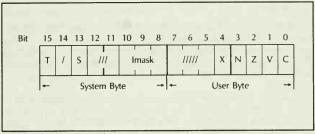

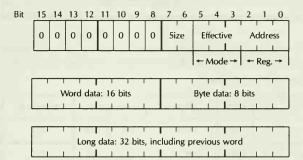

The status register is a 16-bit quantity, organized as shown in Figure 2.3.

Figure 2.3 - Status register layout

#### System Byte

Bits 15–8 are called the *system byte,* because the information contained here is not normally available to applications programs. The fields in the system byte are:

- Bit 15 is a hardware aid for debuggers. It is called the trace bit. If bit 15 is set, an exception will take place at the end of each instruction. Exceptions are described in Chapter 7, Exception Processing. This feature is used by debuggers to regain control as each instruction is executed.

- 2. Bit 13 is used to regulate access to certain instructions and to the system byte of the status register. It is called the *supervisor bit*. If this bit is set, access is allowed. When the supervisor bit is set, the 68000 is said to be executing in *supervisor mode*. When the bit is reset, the 68000 is said to be executing in *user mode*. User mode software is prevented by the hardware from executing certain privileged instructions that might compromise the integrity of the system software. Access to the status register's system byte is also prohibited when in user mode, ensuring that the user mode program cannot change the supervisor bit.

- Bits 10-8 are called the interrupt mask. This feature is more fully explained in Chapter 7, which deals with 68000 exception conditions.

The system byte of the status register is of concern only to systems software programmers. We will deal more extensively with this topic in later chapters.

#### **User Byte**

The lower byte of the status register is called the user byte. The user byte contains a set of bits known as condition codes, which are bit flags used to record the outcome of the last arithmetic operation performed. The user byte can be accessed at any time regardless of machine state. The bits defined in the user byte are:

- The C (carry) bit carries out the high-order bit position of an arithmetic operation. For example, when two 8-bit numbers are added, the C bit is the ninth bit of the result. This bit also receives bits that are shifted out of a number during shift or rotate operations.

- The V (oVerflow) bit is set whenever an operation yields a result that cannot be properly represented. For example, when adding the bytes 7F hex and 01 hex, the result, 80 hex is not properly represented in eight bits. (Remember, 80 hex is – 128 decimal in two's complement notation.) The V bit would be set following such an operation.

- The Z (Zero) bit is set if the result of an operation is zero.

- The N (Negative) bit is set if the high order bit of a result is set. (In two's complement, the high order bit of a number is set if the number is less than zero.)

- The X (eXtended) bit is a copy of the carry bit, but it is not affected by every instruction that affects the carry bit. The purpose of this bit is to facilitate multiprecision instructions. The X bit is affected only by instructions that can be used for multiprecision operations. This allows you to intermix other instructions between multiprecision operations without having to preserve the carry bit.

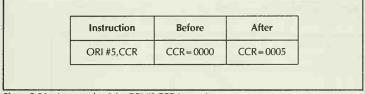

The descriptions of the instruction set in Chapter 3 describe how the condition codes are used by each operation. Since the lower half of the status register contains nothing but the condition codes, it is sometimes called the condition code register (CCR).

## DATA ORGANIZATION IN MEMORY

The 68000 instruction set supports several data formats: binary, BCD, and floating point.

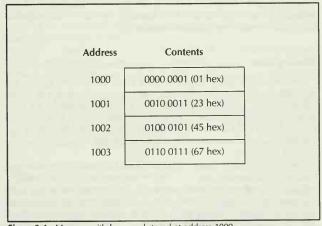

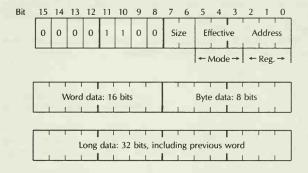

## Bytes, Words, and Longwords

Binary data items can be 8, 16, or 32 bits long. These data types are known as *bytes, words,* and *longwords,* respectively. Most instructions that operate on binary data support any of these three data lengths. For example, the MOVE instruction, which transfers a binary data item from one place to another, has three forms:

- MOVE.B moves a byte of data

- MOVE.W moves a word of data

- MOVE.L moves a longword of data

Note the use of the suffixes .B, .W, and .L to denote data length.

When a word or a longword is stored in memory, the bytes are stored in order of decreasing magnitude. The most significant bits are stored at the lowest address, and the least significant bits are stored at the highest address. For example, when a 16-bit word is stored at location 1000, the most significant byte is at location 1000, and the least significant byte at 1001. When the long word 01234567 (hex) is stored at address 1000, memory appears as shown in Figure 2.4.

Figure 2.4 - Memory with longword stored at address 1000

We emphasize this point because all computers do not store multibyte binary quantities in the same way. In particular, the 8080/Z-80, 6502, and 8086/8088 family of microprocessors store words and longwords in ascending order, so that the low byte is stored at the lowest address and the high byte at the highest address. Which order is "correct" is largely a matter of taste, but you should be aware that the difference exists.

#### BCD

A special form of binary numbers, called *binary* coded decimal (BCD), is often used for digital displays and input devices. The familiar displays on digital clocks and electronic calculators are universally based on BCD. Most computer-based laboratory and factory instruments also use BCD.

BCD is basically hexadecimal without the codes for 10–15 (i.e., A–F). Each nibble represents a digit in a decimal number. Thus, two decimal digits are stored in a byte. The 68000 has instructions for the addition and subtraction of BCD numbers.

BCD is especially useful in commercial applications, such as accounting. Many such applications require only addition and subtraction of numbers in character format. To convert these numbers to binary for calculation and then convert them back to character format for output requires much multiplication and division, which are comparatively slow operations for most computers. Using BCD avoids these expensive operations, and provides quick conversion to and from character format. In many applications, BCD is much more efficient than binary.

## **Floating Point**

Scientific applications require a large range of possible values. For example, to represent Avogadro's number (a common quantity in chemical calculations, roughly 6 followed by 23 zeros) would require ten bytes of storage. To hold the result of the multiplication of two such numbers would require this much storage. Then there is the problem of representing fractional numbers, which none of the data representations thus far have addressed.

The clean solution to these problems is found in floating point numbers. Floating point numbers are a computerized form of scientific notation, which is taught in grade school mathematics. In scientific notation, a number is written as a quantity between 0 and 9 times 10 to the appropriate power. For example, the quantity 1,935,000,000 is written as 1.935  $\times$  10<sup>12</sup>. The quantity 0.000001349 is written as 1.349  $\times$  10<sup>-6</sup>.

Scientific notation is extremely useful in a computer. Allocating a fixed number of bits to the exponent and fraction parts of a number yields a very useful approximation to both very large and very small numbers. The 68000, like most microprocessors, does not directly support floating point with instructions. However, there is an additional feature which can be added to provide hardware support for floating point.

The 68000 add-on is called the 68881 Floating Point Processor. It provides hardware instructions to manipulate floating-point numbers. The 68881 uses a floating-point format known as The Institute of Electrical and Electronic Engineers (IEEE) format, named for the organization that proposed the format as a standard. IEEE format provides the following floating point format:

| S | Exp | Fraction |

|---|-----|----------|

|---|-----|----------|

The field labeled S is the sign bit for the entire number. If this bit is set, the number is negative. If the bit is not set, the number is positive.

The field labeled EXP is the exponent; it is seven bits long. The exponent field indicates the exponent of 2 by which the fractional part of the number is multiplied. To allow for negative exponents, decimal 64 (40 hex) is subtracted from the exponent field before it is used. The exponent range is 00 hex (interpreted as -64) to 7F hex (interpreted as +63). Thus, the range of representation is  $2^{63}$  (approximately 9.2234 ×  $10^{18}$ ) to  $2^{-64}$  (approximately 5.421 ×  $10^{-20}$ ).

The fraction part is 24 bits, or 6–7 decimal digits. This limits the number of significant digits the floating point number may contain. A limit of 6 digits means that the computer cannot correctly subtract 1 from 10,000,000, for example.

Alternate forms of floating point allow more bits for the fraction and exponent to avoid this and other problems with the range and precision of floating-point representation. The remainder of this book deals strictly with integer arithmetic.

#### ASCII

The final form of data storage is known as *ASCII* or character format. ASCII stands for American Standard Code for Information Interchange. This code assigns a numeric value for each character. These values are used to represent characters in memory and during I/O. The current ASCII standard for the United States defines 128 characters, with values from 0–127. The characters are stored one per byte in memory. The eighth bit is used for additional characters in Europe and Japan. For a complete list of United States ASCII values, see Appendix B.

Multicharacter sequences, called *strings* are stored in multiple consecutive bytes in memory. The 68000 provides no instructions explicitly for string manipulation; sequences of byte instructions must be used instead. There are three common types of string storage you may employ:

- Use a fixed length for each string to be stored. This has the advantage of being easy to program, but wastes memory if string length tends to vary. This technique is usually used by the FOR-TRAN and COBOL languages.

- Prefix each string with a character count. This is more difficult to program, but wastes less memory. If the character count is stored in a byte at the beginning of the string, then strings are limited to 255 characters. Using a word (i.e., two bytes) allows 65,535 characters in a string. This is the technique usually used by the Pascal and BASIC languages.

- Terminate the string with some flag value, usually zero. This technique is used by the C language. Problems arise, however, if strings are processed in a manner other than sequentially from beginning to end.

## ADDRESSING MODES

A computer instruction must specify two things:

- 1. What operation to perform, such as addition or subtraction.

- On what data to perform the operation. Data for instructions is usually found either in registers or memory.

A portion of the instruction, called the op code, indicates the operation to perform. The simple example in Chapter 1 used the first digit of the instruction as the op code. Data was in the machine's single register and a memory location. The memory location was identified by the address contained in the last three digits of the instruction. Real computers are seldom so simple. In the 68000, instructions specify operands by one of three techniques:

- Some instructions imply the use of certain operands, usually a register, such as the status register or the Program Counter (PC).

- Some instructions work only on registers. The register number is contained in the instruction itself.

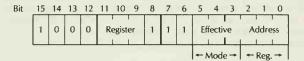

- Most 68000 instructions specify operands with a technique called an effective address. This is a generalized technique for addressing the registers and memory.

#### **Effective Address**

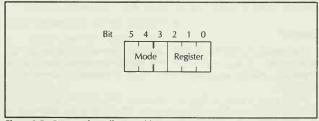

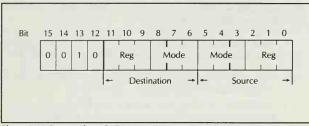

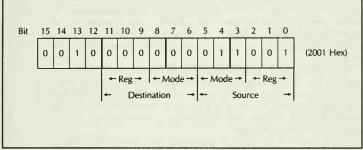

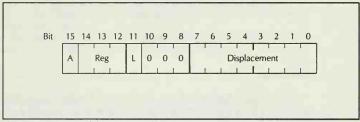

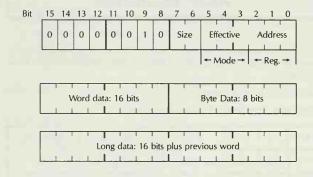

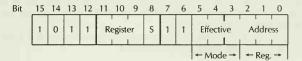

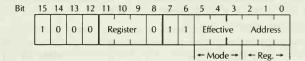

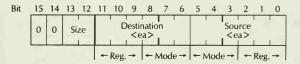

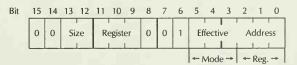

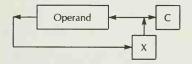

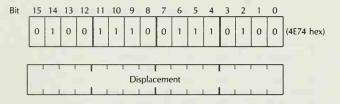

An effective address is specified by six bits in the instruction (usually the lowest six bits). The bit values indicate how to find the data for the instruction. Figure 2.5 shows how these bits are arranged into two groups of three bits.

The mode bits determine the meaning of the entire field. Three bits give eight possible combinations. Values 0–6 mean that a register is to be used, either as the operand, or to determine the address of the operand in memory. If the mode field is 7 (i.e., all 1's), then the entire six bits of the effective address field is used to specify the mode.

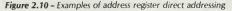

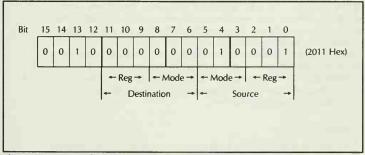

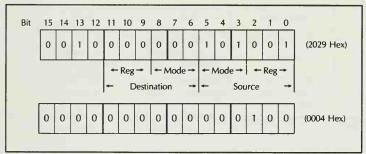

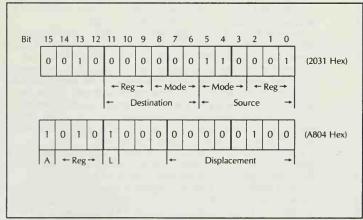

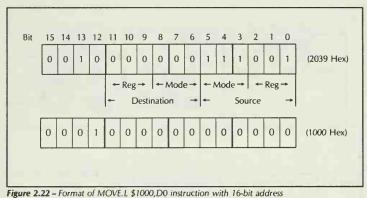

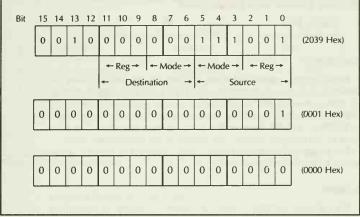

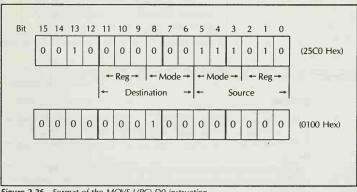

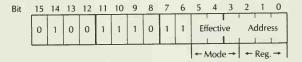

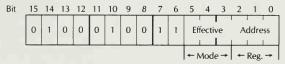

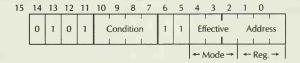

In the following examples, we will illustrate the addressing modes using the *MOVE.L* instruction, which moves a longword from one operand to another. Both operands have the effective address format. We will use the D0.L data register as the destination operand, and vary the source operand to illustrate the various addressing modes. Figure 2.6 shows the format of a *MOVE.L* instruction.

Figure 2.5 - Format of an effective address

Figure 2.6 - Format of a MOVE.L instruction

The Source and Destination fields are used to select the source and destination operands. Since the register and mode fields are three bits wide, it is difficult to look at the hex representation of an instruction and determine the assembly language equivalent. This process is known as *disassembly*. 68000 instructions in general are difficult to disassemble by hand. Fortunately, most debuggers perform disassembly, so this problem is not as severe as it could be.

## **Data Register Direct Addressing**

| Addressing Mode Field: | 000                            |

|------------------------|--------------------------------|

| Register Field:        | 000–111 (Data Register Number) |

| Assembler Syntax:      | Dn (n is 0–7)                  |

#### Description

Data register direct addressing is indicated by an effective address mode field of 000 (binary). The register field contains a number from 000 to 111 (0-7), which indicates a data register. In data register direct addressing, the data register (indicated by the register field) contains the operand.

#### Example

The instruction MOVE.L D1,D0 causes the contents of data register D1 to be copied into data register D0. After the instruction executes, the two registers contain the same information. Figure 2.7 shows the format of this instruction.

When only a word or byte is transferred, the contents of the upper bytes of the data register are unchanged. Figure 2.8 shows examples of the *MOVE* instruction with a byte, a word, and a longword.

Figure 2.7 - Format of MOVE.L D1,D0 instruction

| Instruction  | Before                      | After                        |

|--------------|-----------------------------|------------------------------|

| MOVE.B D1,D0 | D0= FFFFFFF<br>D1= 01234567 | D0= FFFFF67<br>D1= 01234567  |

| MOVE.W D1,D0 | D0= FFFFFFF<br>D1=01234567  | D0= FFFF4567<br>D1= 01234567 |

| MOVE.L D1,D0 | D0= FFFFFFF<br>D1= 01234567 | D0=01234567<br>D1=01234567   |

Figure 2.8 - Moving a byte, word, or longword

## **Address Register Direct Addressing**

Addressing Mode Field:001Register Field:000–111 (Address Register Number)Assembler Syntax:An (n is 0–7)

## Description

Address register direct addressing is indicated by an effective address mode field of 001 (binary). The register field contains a number from 000 to 111 (0-7), which indicates an address register. In address register direct addressing, the address register indicated by the register field contains the operand.

## Example

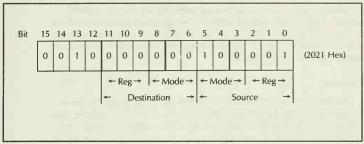

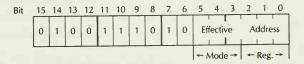

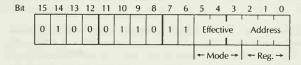

The instruction MOVE.L A1,D0 causes the contents of address register A1 to be copied into data register D0. After the instruction executes, the two registers contain the same information. Figure 2.9 shows the format of this instruction.

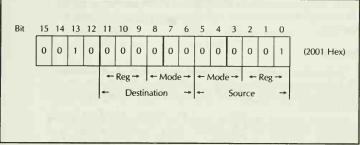

Transfers involving an address register are restricted to word or long size. Byte operations are not allowed. When transferring a word to an address register, bit 15 (the sign bit of a word) is extended throughout the upper word of the address register. Figure 2.10 gives several examples of address register direct addressing.

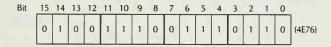

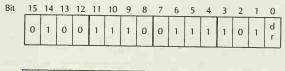

| Bit | 15 | 14 | 13 | 12 | 11 | 10  | 9        | 8     | 7   | 6   | 5   | 4    | 3   | 2   | 1   | 0 |            |

|-----|----|----|----|----|----|-----|----------|-------|-----|-----|-----|------|-----|-----|-----|---|------------|

|     | 0  | 0  | 1  | 0  | 0  | 0   | 0        | 0     | 0   | 0   | 0   | 0    | 1   | 0   | 0   | 1 | (2009 Hex) |

|     |    |    |    |    | +  | Reg | <b>→</b> | - N   | Nod | e → | ← N | Node | e 🛶 | +   | Reg | + |            |

|     |    |    |    |    |    | D   | esti     | natio | n   | >   | -   |      | Sou | rce |     | - |            |

Figure 2.9 - Format of MOVE.L A1, D0 instruction

| Instruction  | Before                       | After                          |

|--------------|------------------------------|--------------------------------|

| MOVE.W A1,D0 | D0= FFFFFFF<br>A1=01234567   | D0== FFFF4567<br>A1== 01234567 |

| MOVE.W D0,A1 | D0= 01234567<br>A1= FFFFFFFF | D0=01234567<br>A1=00004567     |

| MOVE.W D0,A1 | D0=0000FFFF<br>A1=00000000   | D0 = 0000FFFF<br>A1 = FFFFFFFF |

| MOVE.L A1,D0 | D0== FFFFFFFF<br>A1=01234567 | D0=01234567<br>A1=01234567     |

## **Address Register Indirect Addressing**

Addressing Mode Field: Register Field: Assembler Syntax: 010 000-111 (Address Register Number) (An) (n is 0-7)

#### Description

Address register indirect addressing is indicated by an effective address mode field of 010 (binary). The register field contains a number from 000 to 111 (0–7), which indicates an address register.

In address register indirect addressing, the address register indicated by the register field is the address of a memory location that contains the operand. The register is said to point to (contain the address of) the operand. Address register indirection is denoted by enclosing the address register name in parentheses. For example, (A0) denotes indirection on address register A0. Word or longword references require that the address contained in the address register must be even.

#### Example

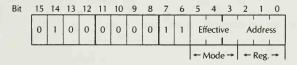

The instruction *MOVE.L* (*A*1),*D*0 causes the contents of the memory location pointed to by address register A1 to be copied into data register D0. After the instruction executes, data register D0 and the memory location contain the same information. Figure 2.11 shows the format of this instruction.

The instruction works as shown in Figure 2.12. \$1000 indicates the contents of the longword in memory at address 1000 hex.

Figure 2.11 - Format of MOVE.L (A1), D0 instruction

| Instruction    | Before          | After           |

|----------------|-----------------|-----------------|

| MOVE.L (A1),D0 | D0 = FFFFFFFF   | D0=01234567     |

|                | A1 = 00001000   | A1 = 00001000   |

|                | \$1000=01234567 | \$1000=01234567 |

Figure 2.12 - An example of the MOVE.L (A1), D0 instruction

#### Address Register Indirect Addressing with Post-Increment

| Addressing Mode Field: | 011                               |

|------------------------|-----------------------------------|

| Register Field:        | 000-111 (Address Register Number) |

| Assembler Syntax:      | (An)+ (n is 0–7)                  |

#### Description

Address register indirect addressing is indicated by an effective address mode field of 011 (binary). The register field contains a number from 000 to 111 (0–7), which indicates an address register. In address register indirect addressing, the address register indicated by the register field contains the address of a memory location that contains the operand. The register is said to point to (contain the address of) the operand.

The address register is incremented after the data has been obtained from memory. The increment is based on the length of the data item referenced by the instruction. Thus, for a *MOVE.B* instruction, the address register would be incremented by one. For a *MOVE.W* instruction, the address register is incremented by two. For a *MOVE.L* instruction, the address register is incremented by four.

Address register indirection with post-increment is denoted by enclosing the address register name in parentheses followed by a plus (+) symbol. For example, (A0)+ denotes post-increment indirection on address register A0. Word or longword references require that the address contained in the address register must be even.

#### Example

The instruction MOVE.L (A1)+, D0 causes the memory location pointed to by address register A1 to be copied into the contents of data register

D0. After the instruction is executed, data register D0 and the memory location contain the same information. Address register A1 is incremented by 4. Figure 2.13 shows the format of this instruction.

The instruction works as shown in Figure 2.14. \$1000 indicates the contents of the longword in memory at address 1000 hex.

A special case occurs when the address register specified is A7, which is the hardware stack pointer. Byte operations on address register A7 cause an increment by two rather than one. This ensures that the stack pointer always contains an even address.

Figure 2.13 - Format of the MOVE.L (A1) +, D0 instruction

| Instruction     | Before                                             | After                                         |

|-----------------|----------------------------------------------------|-----------------------------------------------|

| MOVE.L (A1)+,D0 | D0 = FFFFFFF<br>A1 = 00001000<br>\$1000 = 01234567 | D0=01234567<br>A1=00001004<br>\$1000=01234567 |

Figure 2.14 - An example of the MOVE.L (A1) +, D0 instruction