Application Notes

on the

Atari Computer System Interface (ACSI)

The Atari Corporation

Sunnyvale, California

27 September 1985

# CONFIDENTIAL

|       |       |       |      | ; | 27 | S | ₽ P | te | mt | ) е | T | 1 | 98 | 35 |  |  |  |      |  |      | 12 |

|-------|-------|-------|------|---|----|---|-----|----|----|-----|---|---|----|----|--|--|--|------|--|------|----|

| Tab I | le of | Conte | nts  |   |    |   |     |    |    |     |   |   |    |    |  |  |  |      |  |      |    |

|       |       | Bus . |      |   |    |   |     |    |    |     |   |   |    |    |  |  |  |      |  |      |    |

|       |       | Compl |      |   |    |   |     |    |    |     |   |   |    |    |  |  |  |      |  |      |    |

|       |       | Level |      |   |    |   |     |    |    |     |   |   |    |    |  |  |  |      |  |      | 3  |

|       |       | Level |      |   |    |   |     |    |    |     |   |   |    |    |  |  |  |      |  |      |    |

| 2.    | 3. 1  | _evel | 3    |   |    |   |     |    |    |     |   |   |    |    |  |  |  | <br> |  |      | 7  |

| 3.    | ACSI  | Initi | ator |   |    |   |     |    |    |     |   |   |    |    |  |  |  | <br> |  | <br> | 11 |

# CONFIDENTIAL

THE SCOPE OF THIS DOCUMENT is limited to a set of rough application notes on the Atari Computer System Interface. This is a preliminary document and is subject to change without notice.

#### 1. ACSI Bus

- o control signals and a bidirectional bus.

- o target does not receive a command and hold it pending controller ready an immediate DEVICE NOT READY error must be sent or the initiator will time out and assume controller nonexistent.

- o controller self test recalibrate, ram check, rom checksum, etc.

- o self test always performed following reset -- eliminates need for self test command.

- o initiator could time out (duration to be determined) on a command and reset the target.

- o once the status byte is returned the bus is free.

- o maximum eight bus ports.

- o data transfer rate is up to 8 Mbit/sec.

| Initiator |           |            |                  |

|-----------|-----------|------------|------------------|

|           | •         | 1          | 1                |

|           | Target 0  | Target 1   | Target 7         |

|           |           | ( )<br>( ) |                  |

|           | :Device : | Device     | 1 1              |

|           |           |            | Device    Device |

### CONFIDENTIAL

#### ---- Control and Data Signals -----

| Mnemonic | Name              | Characteristics           |

|----------|-------------------|---------------------------|

|          | Reset             | : TTL levels, active low. |

|          | Address 1         | : TTL levels.             |

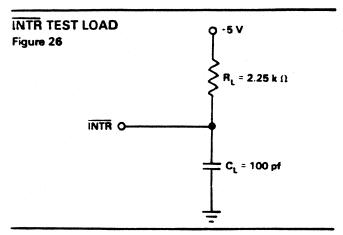

| _IRQ     | Interrupt Request | ! TTL levels, active low, |

| 1        |                   | : 1 Kohm pullup on        |

| 1        |                   | initiator side.           |

| _CS      | Chip Select       | ! TTL levels, active low. |

| ! R/_W : | Read/Write        | : TTL levels.             |

| _DRQ     | Data Request .    | ! TTL levels, active low, |

| 1 1      | <u>-</u>          | : 1 Kohm pullup on        |

| 1        |                   | ! initiator side.         |

| I ACK I  | Acknowledge       | ! TTL levels, active low. |

|          | Data Bus (0-7)    | : TTL levels.             |

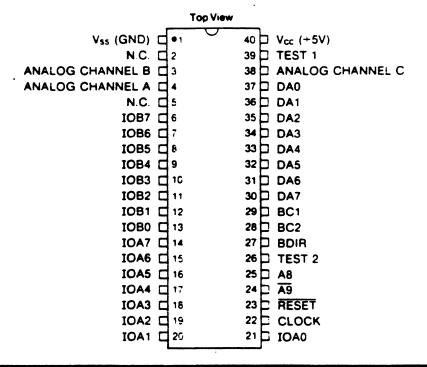

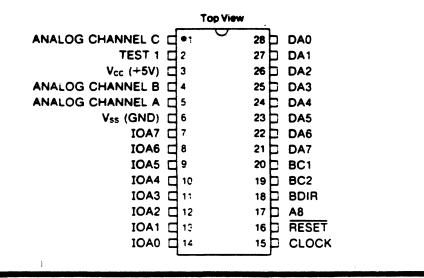

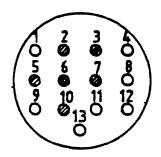

#### ---- Initiator ACSI Port Pin Assignments -----

| INITIATOR | DB 19S                  | TARGET     |

|-----------|-------------------------|------------|

|           | 1 :< Data 0>            | 1          |

|           | 2   ( Data 1)           | •          |

|           | 3 !< Data 2>            | 1.         |

|           | 4 (< Data 3>            | 1          |

|           | 5 ( Data 4>             | 1          |

|           | 6 (< Data 5>            | 1          |

|           | 7 ( Data 6)             | 1          |

|           | 8 (< Data 7>            | . 1        |

|           | 9                       | 1          |

| •         | 10 :< Interrupt Request | . ]        |

|           | 11   Ground             |            |

|           | 12   Reset>             | . 1        |

|           | 13 ! Ground             | -1         |

|           | 14 : Acknowledge        | · <b>{</b> |

|           | 15 : Ground             |            |

|           | 16 : A1                 | •          |

|           | 17 : Ground             | . ;        |

|           | 18                      | . 1        |

|           | 19                      | . }        |

|           | 40 00 00 00             |            |

# CONFIDENTIAL

#### 2. ACSI Compliance

#### 2.1. Level 1

- o target will speak only when spoken to.

- o listen to bus during idle -- no disconnect.

- o abort initiator via interrupt.

- o abort target via reset -- software reset must be provided in initiator.

- o RESET HOLD TIME is 12 microseconds.

- o reset has highest bus priority.

- o reset cannot be asserted by a target whether active or inactive.

- o 100 milliseconds before initiator times out on target acknowledgement.

- o CAVEAT: if an initiator prematurely issues a command while the target is executing a command, then the results are unpredictable.

- o device driver in initiator will wait until status byte is returned -- otherwise time out (TBD) and reset target.

- o after receipt of command byte, transaction belongs to controller.

- o target has complete control of bus until status byte is returned.

- o each target should have a user select controller number.

### CONFIDENTIAL

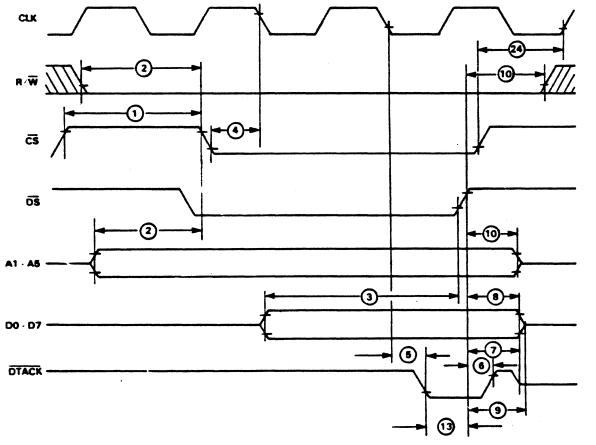

HARDWARE.

| (       | Command Phase     | ******************                                                                                             |    |              |

|---------|-------------------|----------------------------------------------------------------------------------------------------------------|----|--------------|

| Data di | irection: FROM in | itiator TO target.                                                                                             |    |              |

| A1      |                   | ti antan manan | ./ |              |

| IRQ     |                   |                                                                                                                |    |              |

| _cs     | :                 | /                                                                                                              |    |              |

| R/_W    |                   | <u> </u>                                                                                                       |    | _/           |

| DATA    | 1                 | 1                                                                                                              |    | 1            |

|         | Byte O            | p>;<- <b>c</b> ->;                                                                                             |    | <b>-</b> , ; |

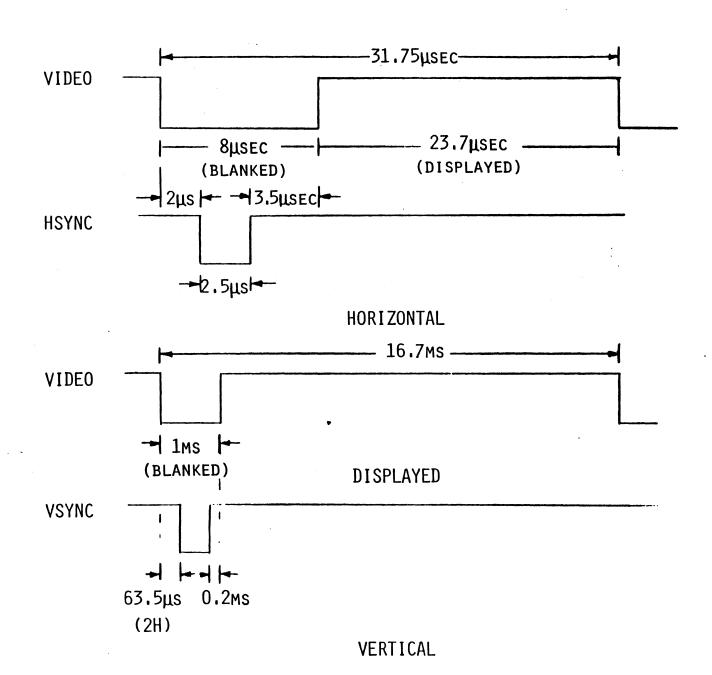

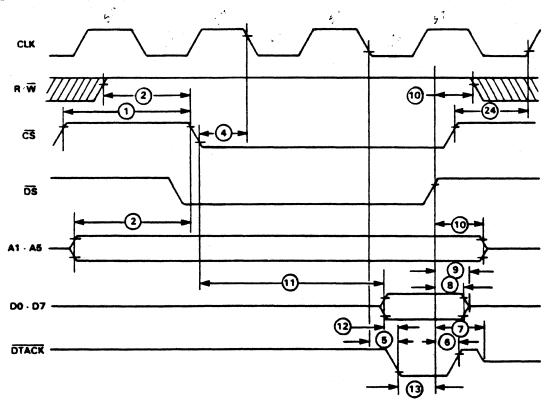

Timing

- a) 60 ns (max)

- b) 250 ns (max)

- c) 20 ns (max)

# CONFIDENTIAL

|       | Status Phase                                                  |

|-------|---------------------------------------------------------------|

| Data  | direction: FROM target TO initiator.                          |

| A1    |                                                               |

| IRG   |                                                               |

| _cs   |                                                               |

| R/_W  |                                                               |

| DATA  | ===========> <valid>&lt;===<br/> </valid>                     |

|       | Byte O                                                        |

| Timir | a) 50 ns (max) b) 150 ns (max) c) 100 ns (max) d) 80 ns (max) |

|       | SOFTWARE.                                                     |

|       | Controller Select Byte                                        |

|       | Byte O :xxx:                                                  |

|       | - Completion Status Byte                                      |

|       | 70L = 70 I                                                    |

# CONFIDENTIAL

# 2.2. Level 2 o include Level 1. o TEST UNIT READY

o TEST UNIT READY command is used as a poll.

o NO ERROR is to be interpreted as controller ready.

o DEVICE NOT READY is to be interpreted as controller not ready.

SOFTWARE.

---- Command Descriptor Byte -----

---- Command Summary Table -----

OpCode | Command | Command | CoxOO | Test Unit Ready |

---- Completion Status Byte -----

Device Errors

0x00 No Error 0x04 Device Not Ready

Miscellaneous Errors

0x30 Controller Self Test Failed

### CONFIDENTIAL

#### 2.3. Level 3

o include Level 1 and Level 2.

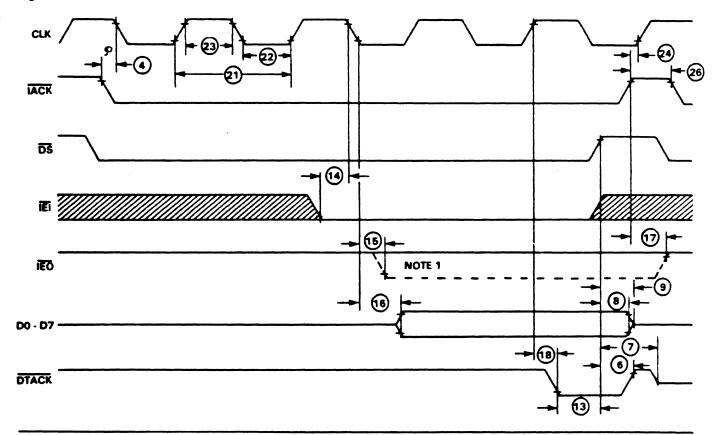

HARDWARE.

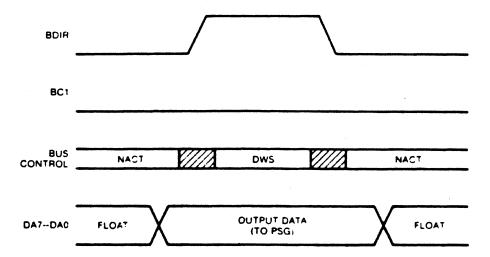

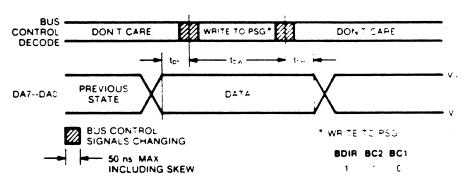

---- Data Out Phase -----

Data direction: FROM initiator TO target.

A1 .

| <-a-> | <-

Timing

- a) 60 ms (max)

- b) 250 ns (max)

- c) 240 ns (max)

- d) 240 ns (min)

### CONFIDENTIAL

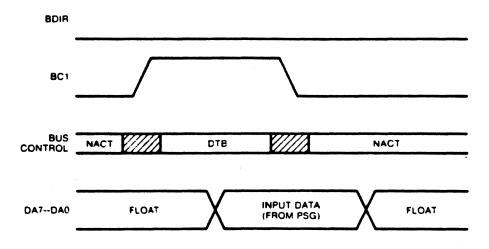

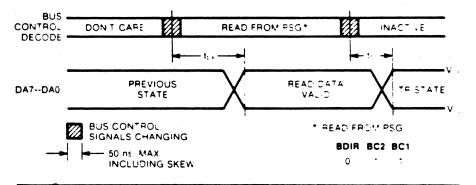

| D       | ata In Pha | se                        |            |                                   |   |

|---------|------------|---------------------------|------------|-----------------------------------|---|

| Data di | rection:   | FROM targe                | t TO initi | ator.                             |   |

| A1      | •          |                           | ·          | •                                 | - |

| DRQ     | :\         |                           |            |                                   | - |

| _ACK    |            |                           |            | _/                                | - |

| DATA    | :          | ><<br>                    |            | ;<br>><====<br> <br> <br>>!<-c->! | = |

| Timing  |            | (max)<br>s (max)<br>(min) |            | •                                 |   |

# CONFIDENTIAL

SOFTWARE.

```

---- ACSI Command Descriptor Block -----

Byte O

| | xxxxxxxx |

1111111

!!! ----- Operation Code

---- Controller Number

Byte 1

!xxxxxxxx!

1111111

!!! ----- Block Address High ---- Device Number

Byte 2

!xxxxxxxx!

11111111

---- Block Address Mid

Byte 3

!xxxxxxxx!

---- Block Address Low

Byte 4

!xxxxxxxx!

----- Block Count

Byte 5

!xxxxxxxx!

11111111

----- Control Byte

```

---- Command Summary Table -----

| ļ  | OpCode | 1 | Command         | 1 |   |

|----|--------|---|-----------------|---|---|

| •  |        |   |                 |   |   |

| i  | 0x00   | : | Test Unit Ready | į |   |

| ;  | 0x08   | ł | Read            | ŧ | ¥ |

| ŀ  | 0x0a   | 1 | Write           | ŀ | ¥ |

| :  | OxOb   | : | Seek            | 1 |   |

| ŀ  | Oxia   | • | Mode Sense      | i |   |

| ٠, |        |   |                 | ` |   |

\* multisector transfer with implied seek

### CONFIDENTIAL

#### Command Errors

| 0x20 | Invalid Command       |

|------|-----------------------|

| 0x21 | Invalid Address       |

| 0x23 | Volume Overflow       |

| 0x24 | Invalid Argument      |

| 0x25 | Invalid Device Number |

# CONFIDENTIAL

#### 3. ACSI Initiator

- o must transfer data in 16 byte increment blocks.

o must use ST BIOS system variable flock (see A Hitchhiker's Guide to the BIOS).

- ---- Initiator Handshake Sequence -----

- o load DMA Base Address Register.

- o toggle Write/\_Read to clear status (DMA Mode Control Register).

- o select DMA read or write (DMA Mode Control Register).

- o select DMA Sector Count Register (DMA Mode Control Register).

- o load DMA Sector Count Register (DMA operation trigger).

- o select controller internal command register (DMA Mode Control Register).

- o issue controller select byte by clearing AO to O.

- o set AO to 1 for remaining command bytes.

- o after last command byte select controller (DMA Mode Control Register).

- o DMA active until sector count is zero (DMA Status Register, do not poll during DMA active).

- o check DMA error status (DMA Status Register).

- o check controller status byte.

### CONFIDENTIAL

```

; nonzero for loadable driver

loadable

egu

ST SASI hard disk driver

(C)1985 Atari Corp.

Hacked it up. "Gee, it seems to work . . . "

* 9-Apr-1985 1md

* 14-Apr-1985 lmd

linked with BIOS (***FOR NOW***)

hacked for WD controller (now, wired...)

* 20-Apr-1985 1md

* 24-Jun-1985 jwt

hacked for Adaptec, new kludge board

* 01-Jul-1985 jut

seems to work, add more formatting and more

detailed error reporting

* 22-Jul-1985 jut

change timing of wdc/wdl at start of command.

added extra move. w $8a, wdl to change A1

* 23-Jul-1985 jut

use a move. 1 instruction for all wdc/wdl write

pairs since it changes Al quickly enough that

the (old) DMA chip does not incorrectly

generate two chip selects

flock

$43e

; FIFO lock variable

equ

hdv_init

$46a

; hdv_init()

equ

hdv_bpb

$472

; hdv_bpb(dev)

equ

$476

hdv_rw

; hdv_rw(rw, buf, count, recno, dev)

equ

hdv_boot

$47a

i hdv_boot()

equ

hdv_mediach

$47e

; hdv_mediach(dev)

equ

_drvbits

$4c2

; block device bitVector

equ

_dskbufp

$4c6

; pointer to common disk buffer

equ

nretries

3

equ

; #retries-1

----- Installer -

.globl i_sasi

i_sasi: bra

i_sasi2

dc.b '@(#)ahdx v0.04',$0d,$0a,0,$1A

----- Front End -----

LONG hbpb(dev) - return ptr to BPB (or NULL)

* Passed:

4(sp). W

*-

hbpb:

move. \omega 4(sp), d0

; dO = devno

move. I o_bpb, aO

; aO -> pass-through vector

```

```

Sep 26 11:55 1985 ahdx.s Page 2

_sasi_bpb(pc),a1

; a1 -> our handler

lea

; do it

bra

check_dev

*+

* LONG rw(rw, buf, count, recno, dev)

* Passed:

$e(sp). W

dev

recno

$c(sp). W

$a(sp).W

count

6(sp). L

buf

4(sp). W

TW

hrw:

move.w $e(sp),dO

; d0 = devno

move. 1 o_rw.a0

; aO -> pass-through vector :

_sasi_rw(pc),a1

. lea

; a1 -> our handler

; do it

bra

check_dev

* LONG mediach(dev)

dev 4(sp). W

* Passed:

hmediach:

move. w 4(sp), dO

; dO = devno

move.l o_mediach,aO

; aO -> pass-through vector

o_megiach.au ; aO -> pass-throug

_sasi_mediach(pc).a1 ; a1 -> our handler

·lea

* check_dev - use handler, or pass vector through

* Passed:

dO.w = device#

aO -> old handler

ai -> new handler

a5 -> $0000 (zero-page ptr)

* Jumps-to: (a1) if dev in range for this handler

(a0) otherwise

*

check_dev:

#2, d0

i devnos match?

cmp. w

```

\* ----- Medium level driver -----

bne

chkd\_f: \_mp

chkd\_f

(a0)

move. l al, aO

; do it

; yes -- follow success vector

```

*+

_sasi_init - initialize SASI dev

* Passed:

nothing

* Returns:

dO < 0: error

dO ==O: success

* function performed by \underline{\hspace{0.1cm}} hinit... and the assembler won't

let me have a forward reference here

.globl _sasi_init

*_sasi_init: equ

_hinit

*+

_sasi_bpb - return BPB for hard drive

LONG _sasi_bpb(dev)

* Synopsis:

WORD devi

NULL, or a pointer to the BPB buffer

* Returns:

.globl

_sasi_bpb

_sasi_bpb:

#thebpb,dO

move. 1

rts

_sasi_rw - read/write hard sectors

Synopsis:

_sasi_rw(rw, buf, count, recno, dev)

* Passed:

dev

$e(sp). W

$c(sp). W

recno

$a(sp). W

count

*

buf

6(sp). L

4(sp). W

; non-zero -> write

TW

.globl

_sasi_rw

_sasi_rw:

move. w #nretries, retrycnt

; setup retry counter

; coerce word to long, unsigned

sasrw1: moveq

#0, d0

move. w

$c(sp), d0

; sect.L

move. w

$a(sp), d1

; count. W

move. 1

6(sp), d2

; buf. L

move. w

4(sp), d3

clr. w

; dev = 0

-(sp)

move. 1

d2, -(sp)

; buf

move. w

d1, -(sp)

; count

move. 1

dO_{i} - (sp)

tst. w

dЗ

; read or write?

bne

sasrw3

; (write)

_hread

bsr

; read sectors

sasrw2

bra

sasrw3: bsr

_hwrite

; write sectors

```

```

Sep 26 11:55 1985 ahdx.s Page 4

```

```

sasrw2: add.w

; (cleanup stack)

#12, sp

tst. 1

dО

; errors?

; no -- success

beq

sasrwr

subq. w

#1, retrycnt

; drop retry count and retry

bpl

sasrw1

sasrwr: rts

*+

_sasi_mediach - see if hard disk media has changed (it never does)

_sasi_mediach(dev)

* Synopsis:

WORD devi

* Returns:

OL

_sasi_mediach

.globl

_sasi_mediach:

clr. 1

dΟ

rts

* BPB for 10MB drive

* Approximate only. Tweak me.

thebpb: dc.w

512

; #bytes/sector

dc. w

2

; #sectors/cluster

dc.w

1024

; #bytes/cluster

i rdlen (256 root files) (in sectors)

dc. w

. 16

dc. w

41

; FATsiz (10300 FAT entries) (sectors)

dc.w

42

; 2nd FAT start

dc. w

99

; data start (in sectors)

dc. w

10300

; #clusters (approximate here)

dc. w

; flags (16-bit FATs)

----- Low-level driver -----

*---- Globals

; FIFO lock variable

flack

$43e

equ

; 200hz system ticker

_h z _200

$4ba

equ

*---- Hardware:

wdc

$ff8604

equ

wd 1

$ff8606

equ

wdcwd1

wdc

; used for long writes

equ

dmahi

$ff8609

equ

dmamid

dmahi+2

equ

```

```

Sep 26 11:55 1985 andx s Page 5

dmalow

equ

dmamid+2

gpip

equ

$fffa01

*---- Tunable:

ltimeout

$80000

; long-timeout

equ

stimeout

equ

$80000

; short-timeout

*+

* LONG gdone() - Wait for operation complete

* Passed:

nathina

EQ: no timeout

* Returns:

MI: timeout condition

* Uses:

DO

_qdone:

move. 1

#ltimeout, tocount

qd1:

#1, tocount

; drop timeout count

subq. 1

; (i give up, return NE)

bmi

qdq

move. b

gpip, dO

; interrupt?

and b

#$20, d0

bne

; (not yet)

qd1

moveq

#0, d0

; return EQ (no timeout)

qdq:

rts

# WORD _endcmd()

* Wait for end of SASI command

* Passed:

dO value to be written to wdl

* Returns:

EQ: success (error code in DO. W)

MI: timeout

NE: failure (SASI error code in DO.W)

* Uses:

dO. d1

*-

_endcmd: move

dO, d1

; preserve wdl value

_qdone

; wait for operation complete

bsr

bmi

; (timed-out, so complain)

endce

d1, wdl

move. w

nop

MOVe. w

wdc, dO

; get the result

and. w

#$00ff, d0

; (clean it up), if non-zero should

```

### \*+ \*-\_hinit(dev)

endce: rts

### CONFIDENTIAL

; do a ReadSense command to learn more

```

Sep 26 11:55 1985 ahdx.s Page 6

* WORD dev;

* Initialize hard disk

* Returns:

-1 if hard disk not there

*

*-

_sasi_init

.globl

_sasi_init:

_hinit:

pea

actur

; push test unit read command block adr

bsr

_dosahdxc

addq. 1 #4, sp

rts

* _hread(sectno, count, buf, dev)

* LONG sectno;

4(sp)

* WORD count;

8(sp)

* LONG buf;

$a(sp)

$b=high, $c=mid, $d=low

* WORD dev;

$e(sp)

* Returns:

-1 on timeout

O on success

*

*

nonzero on error

¥--

.globl

_hread

_hread:

st

flock

; lock FIFO

#$88, wd1

move

#$0008008a, wdcwdl

; OB wdc, 8a wdl

move. 1

move. 1

$a(sp),-(sp)

; set DMA address

bsr

_setdma

#4, sp

addq

; set sector and size

bsr

_setss

bmi

_hto

#$190, wd 1

move. w

nop

#$90, wd1

move. w

nop

move. w

8(sp), wdc

; write sector count to DMA chip

nop

move. w

#$8a, wd l

nop

move. l

#$0000000, wdcwd1

; control byte O wdc O wdl

#$8a, d0

move. w

```

### CONFIDENTIAL

; cleanup after IRQ

bsr

bra

hrx:

\_endcmd

\_hdone

```

* _hwrite(sectno, count, buf, dev)

* LONG sectno;

4(sp)

* WORD count;

8(sp)

* LONG buf;

$b=high, $c=mid, $d=low

$a(sp)

* WORD devi

$e(sp)

*-

.globl _hwrite

_hwrite:

; lock FIFO

st

flock

; set DMA address

$a(sp),-(sp)

move. 1

_setdma

bsr

#4, sp

addq

move. w #$88, wd1

move. 1

#$000a008a, wdcwd1

; Oa wdc 8a wdl

bsr

setss

bmi

_hto

#$90, wd1

move. w

nop

move. w #$190, wdl

nop

; sector count for DMA cr

move. w 8(sp), wdc

nop

move. w #$18a, wdl

nop

move. 1 #$00000100, wdcwdl

move. w #$18a, dO

bsr

_endcmd

; cleanup after IRQ

hwx:

bra

_hdone

* _wd_format - format WD hard disk

* Passed:

nothing

0, or -N

* Returns:

* Uses:

<...>

¥

_wd_format

.globl

_wd_format: lea acfmt,aO

; pick up pointer to the

clr.w

dΟ

flock

st

; lock FIFO

move. w

#$88, wd1

(a0)+,d0

move. b

; get the command byte

swap

dΟ

#$8a, d0

move. w

move. 1

dO, wdc

; byte wdc 8a wdl

moveq

#(5-1), d1

; write remaining 5 byte

```

```

nt1:

(presumes only one unit)

bsr

_qdone

bmi

_h to

(a0)+,d0

; next byte of command

move. b

dO

swap

#$8a, dO

move. w

move. 1

dO, wdcwdl

dbra

d1, fmt1

nt2:

btst

#5, gp.ip

; wait (forever) for completion

bne

fmt2

wdc, dO

move. w

; get the status

#$00FF, d0

andi.w

; only low byte is significant

; cleanup after IRQ

bra

_hdone

_wd_setup - setup parameters for WD hard disk

.globl

_wd_setup

wd_setup:

st

flock

pea

adap_parms(pc)

_setdma

bsr

#4, sp

addq

#$88, wd l

move. w

move. 1

#$0015008a, wdcwdl

; mode select command 15 wdc 8a wdl

_qdone

bsr

bmi

wd x

#$0000008a, wdcwdl

move. 1

_qdone

bsr

bmi

wdx

move. 1

#$0000008a, wdcwd1

_qdone

bsr

bmi

wd x

move. 1

#$0000008a, wdcwd1

bsr

_qdone

bmi

wd x

move. 1

#$0016008a, wdcwd1

; 22 bytes of parameters

_qdone

bsr

bmi

wd x

move. w

#$90, wd1

; reset the DMA chip

nop

#$190, wd1

move. w

nop

#$01, wdc '

; i sector of DMA (actually less)

move. w

nop

move.w #$18a,wdl

nop

move. l

#$00000100, wdcwdl

; control byte

move. w

#$18a,d0

; wdl value

```

```

Sep 26 11:55 1985 ahdx. s Page 9

bsr

endcmd

_hdone

wdx:

bra

*--- parameters for 10MB WD

$02,$00,$01,$02,$62,$02,$01,$00,$01,$00,$00,$02

dc. b

*+

* LONG _dosahdxc( addr ) BYTE *addr;

do a simple (no DMA) ahdx command

_dosahdxc

.globl

_dosahdxc: movea.l 4(sp),a0

; pick up pointer to the command block

clr.w

dO

; lock FIFO

st

flock

move. w

#$88, wd1

(a0)+, d0

; get the command byte

move. b

d0

swap

#$8a, d0

move. w

; send it to the controller

move. 1 dO, wdcwdl

#(5-1),d1

; write remaining 5 bytes of command

moveq

_qdone

dosac1: bsr

(presumes only one unit)

_h to

bmi

move. b

(a0)+, d0

; next byte of command

swap

dΟ

move. w

#$8a, dO

move. 1

dO. wdcwdl

dbra

d1, dosac1

_qdone

bsr

; wait for the command to complete

bmi

hto

move.w wdc,dO

; get the status

#$00FF, d0

andi.w

; only low byte is significant

bra

; cleanup after IRQ

_hdone

* void _setdma(addr)

* LONG addr;

_setdma:

move. b

7(sp), dmalow

6(sp), dmamid

move. b

move. b

5(sp), dmahi

rts

* WORD _setss

-- set sector number and number of sectors

```

### CONFIDENTIAL

\_setss: move.w #\$8a,wdl

```

; wait for controller to take command

bsr

_qdone

bmi

setsse

; construct sector#

9(sp), d0

move. b

move. b

$e(sp), d1

; ORed with devno

lsl.b

#5, d1

or. b

d1, d0

dO

swap

#$008a, d0

move. w

move. 1

dO, wdcwd1

; write MSB sector# + devno

_qdone

bsr

bmi

setsse

move. b

10(sp), d0

; write MidSB sector#

swap

dΟ

move. w

#$008a, d0

move. 1

dO, wdcwd1

bsr

_qdone

bmi

setsse

move. b

11(sp), dO

; write LSB sector#

dO

swap

#$008a, d0

move. w

move. 1 dO, wdcwdl

_qdone

bsr

bmi

setsse

move. w

12(sp), d0

; write sector count

swap

dO

#$008a, d0

move. w

move. 1

dO, wdcwd1

_qdone

bsr

setsse: rts

hto:

moveq

#-1, dO

; indicate timeout

_hdone: move.w #$80,wd1

; Landon's code seems to presume we

пор

put this back to $80

tst. w

wdc

clr

flock

; NOW, signal that we are done

rts

dc. 1

; (saved SSP)

savssp:

dc. 1

; timeout counter

tocount:

1

dc. w

; retry counter

retrycnt:

1

dc. 1

1

o_init:

dc. 1

1

o_bpb:

O_rw:

dc. 1

1

o_mediach:

dc. 1

i_sasi2: nop

ifne loadable

clr. 1

-(sp)

; it's a bird...

move. w

#$20,-(sp)

... it's a plane ...

... no, its:

trap

#1

CONFIDENTIAL

```

```

Sep 26 11:55 1985 ahdx.s Page 11

```

```

; SOOUPERUSER!

addq

#6, sp

move. 1

dO, savssp

; "Faster than a prefetched opcode..."

endc

bsr

_sasi_init

; kick controller

tst. w

dO

bne

isase

; punt -- disk didn't respond correctly

clr. 1

dO

_drvbits,d0

or. 1

; include C: bit in devVector

#$4, dO

or. 1

move. 1

dO, _drvbits

clr. 1

; zeropage ptr

move. 1

hdv_bpb(a5).o_bpb

; save old vectors

move. l

hdv_rw(a5), o_rw

move. 1

hdv_mediach(a5).o_mediach

move. 1

#hbpb,hdv_bpb(a5)

; install our new ones

move. 1

#hrw.hdv_rw(a5)

move. 1

#hmediach.hdv_mediach(a5)

isasq:

nop

; stupid assembler

ifne loadable

move. 1

savssp, -(sp)

; become a mild mannered user process

move. w

#$20, -(sp)

trap

#1

addq

#6, Sp

endc

ifne loadable

move. w

#O, -(sp)

; exit code

move. 1

#((i_sasi2-i_sasi)+$0100),-(sp); save code, data, & basepage

#$31,-(sp)

; terminate and stay resident

MOVE. W

; should never come back...

trap

#1

endc

rts

isase:

lea

nodmsg, a0

bsr

msg

ifne loadable

move. 1

savssp, -(sp)

; become a mild mannered user process

move. w

#$20,-(sp)

trap

#1

addq

#6, sp

endc

#1, -(sp)

move. w

; flag error status

move. w

#$4c,-(sp)

; terminate

#1

trap

msg:

move. 1

aO, -(sp)

move. w

#9,-(sp)

; print null terminated string

```

Sap 26 11:55 1985 ahdx.s Page 12

trap #1

addq. 1 #6, sp

rts

actur: dc.b 0,0,0,0,0,0 acfmt: dc.b 4,0,0,1,0

; atari command: test unit ready

format disk

nodmsg: dc.b

'No AHDX disk response.',\$0d,\$0a,0

. even

end

MC6850 (1.0 MHz) MC68A50 (1.5 MHz) MC68B50 (2.0 MHz)

#### ASYNCHRONOUS COMMUNICATIONS INTERFACE ADAPTER (ACIA)

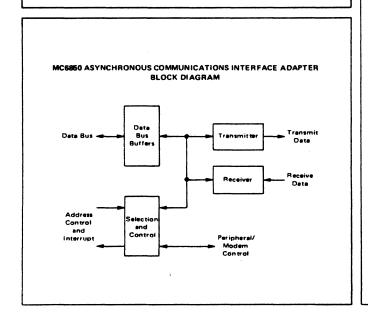

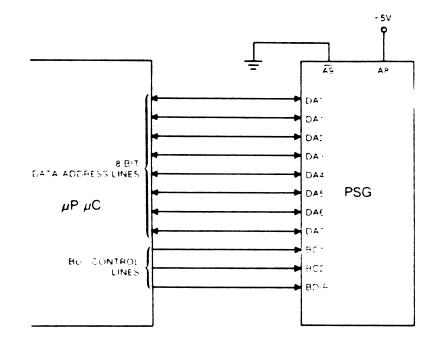

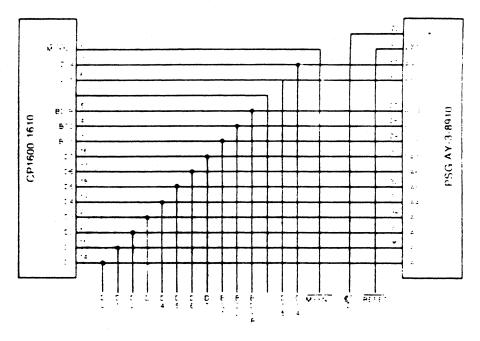

The MC6850 Asynchronous Communications Interface Adapter provides the data formatting and control to interface serial asynchronous data communications information to bus organized systems such as the MC6800 Microprocessing Unit.

The bus interface of the MC6850 includes select, enable, read/write, interrupt and bus interface logic to allow date transfer over an 8-bit bidirectional data bus. The parallel data of the bus system is serially transmitted and received by the asynchronous data interface, with proper formatting and error checking. The functional configuration of the ACIA is programmed via the data bus during system initialization. A programmable Control Register provides variable word lengths, clock division ratios, transmit control, receive control, and interrupt control. For peripheral or modem operation, three control lines are provided. These lines allow the ACIA to interface directly with the MC6860L 0-600 bps digital modem.

- 8- and 9-Bit Transmission

- Optional Even and Odd Parity

- Parity, Overrun and Framing Error Checking

- Programmable Control Register

- Optional +1, +16, and +64 Clock Modes

- Up to 1.0 Mbps Transmission

- False Start Bit Deletion

- Peripheral/Modern Control Functions

- Double Buffered

- One- or Two-Stop Bit Operation

### MOS

(N-CHANNEL, SILICON-GATE)

ASYNCHRONOUS

COMMUNICATIONS INTERFACE

ADAPTER

#### **MAXIMUM RATINGS**

| Characteristics                                                                        | Symbol           | Value                                                     | Unit |

|----------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------|------|

| Supply Voltage                                                                         | Vcc              | -0.3 to +7.0                                              | ٧    |

| Input Voltage                                                                          | V <sub>in</sub>  | -0.3 to $+7.0$                                            | V    |

| Operating Temperature Range<br>MC6850, MC68A50, MC68B50<br>MC6850C, MC68A50C, MC68B50C | TA               | T <sub>L</sub> to T <sub>H</sub><br>0 to 70<br>-40 to +85 | °C   |

| Storage Temperature Range                                                              | T <sub>stq</sub> | - 55 to + 150                                             | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either VSS or VCC).

#### THERMAL CHARACTERISTICS

| Characteristic                            | Symbol | Value           | Unit |

|-------------------------------------------|--------|-----------------|------|

| Thermal Resistance Plastic Ceramic Cerdip | θJA    | 120<br>60<br>65 | °C/W |

#### **POWER CONSIDERATIONS**

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

(1)

Where:

TA = Ambient Temperature, °C

θJA≡Package Thermal Resistance, Junction-to-Ambient, °C/W

PD=PINT+PPORT

PINT = ICC × VCC, Watts - Chip Internal Power

PPORT = Port Power Dissipation, Watts - User Determined

For most applications PPORT < PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$P_D = K + (T_J + 273$ °C)

(2)

Solving equations 1 and 2 for K gives:

$K = PD \cdot (TA + 273 \circ C) + \theta JA \cdot PD^2$

(3)

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring PD (at equilibrium) for a known TA. Using this value of K the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

#### DC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5.0 Vdc ±5%, V<sub>SS</sub> = 0, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub> unless otherwise noted )

| Characteristic                                                                                                    |                                                        | Symbol           | Min                | Тур       | Max         | Unit |

|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|--------------------|-----------|-------------|------|

| Input High Voltage                                                                                                | , t                                                    | VIH              | VSS + 2.0          | -         | Vcc         | ٧    |

| Input Low Voltage                                                                                                 |                                                        | VIL              | VSS-0.3            | -         | VSS+0.8     | ٧    |

| Input Leskage Current<br>(Vin = 0 to 5.25 V)                                                                      | R/W, CS0, CS1, CS2, Enable<br>RS, Rx D, Rx C, CTS, DCD | lin              | -                  | 1.0       | 2.5         | μА   |

| Three-State (Off State) Input Current (Vin = 0.4 to 2.4 V)                                                        | D0-D7                                                  | <sup>I</sup> TSI | -                  | 2.0       | 10          | μА   |

| Output High Voltage (ILoad = - 205 µA, Enable Pulse Width < 25 µs) (ILoad = - 100 µA, Enable Pulse Width < 25 µs) | D0-D7 Tx Data, RTS                                     | ∨он              | VSS+2.4<br>VSS+2.4 | -         | -           | v    |

| Output Low Voltage (ILoad = 1.6 mA, Enable Pulse Wi                                                               | dth < 25 µs)                                           | VOL              | -                  | _         | VSS+0.4     | V    |

| Output Leakage Current (Off State) (VOH = 2.4 V)                                                                  | IRO                                                    | ILOH             | -                  | 1.0       | 10          | μA   |

| Internal Power Dissipation (Measured at TA = TL)                                                                  |                                                        | PINT             | -                  | 300       | 525         | mW   |

| Internal Input Capacitance  (Vin = 0, TA = 25°C, f = 1.0 MHz)  E, Tx CLK, Rx CLK, R/W, RS, Rx Da                  | DO-D7<br>eta, CS0, CS1, CS2, CTS, DCD                  | Cin              | _                  | 10<br>7.0 | 12.5<br>7.5 | pF   |

| Output Capacitance<br>(V <sub>in</sub> = 0, T <sub>A</sub> = 25°C, f = 1.0 MHz)                                   | RTS, Tx Data<br>IRQ                                    | Cout             | -                  | -         | 10<br>5.0   | pF   |

#### SERIAL DATA TIMING CHARACTERISTICS

| Characteristic                                             |                  | Symbol | MC  | MC6850 |     | MC68A50 |     | MC68B50 |      |

|------------------------------------------------------------|------------------|--------|-----|--------|-----|---------|-----|---------|------|

|                                                            |                  | Symbol | Min | Max    | Min | Max     | Min | Max     | Unit |

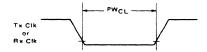

| Data Clock Pulse Width, Low                                | + 16, + 64 Modes | PWCI   | 600 | -      | 450 | _       | 280 | _       |      |

| (See Figure 1)                                             | + 1 Mode         | LAACE  | 900 | -      | 650 | -       | 500 | -       | ns   |

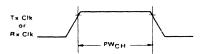

| Data Clock Pulse Width, High                               | + 16, + 64 Modes | PWCH   | 600 | -      | 450 | -       | 280 | -       | ns   |

| (See Figure 2)                                             | + 1 Mode         | LAACH  | 900 | _      | 650 |         | 500 | _       | 115  |

| Data Clock Frequency                                       | + 16, + 64 Modes | fc     | -   | 0.8    | -   | 1.0     | _   | 1.5     | MHz  |

|                                                            | + 1 Mode         | ,,,    | -   | 500    | -   | 750     | _   | 1000    | kHz  |

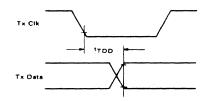

| Data Clock-to-Data Delay for Transmitter (See Figure 3)    |                  | tTDD   | -   | 600    | -   | 540     | -   | 460     | ns   |

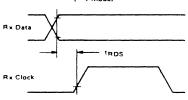

| Receive Data Setup Time (See Figure 4)                     | + 1 Mode         | TRDS   | 250 | -      | 100 | -       | 30  | -       | ns   |

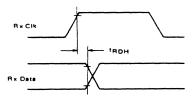

| Receive Data Hold Time (See Figure 5)                      | + 1 Mode         | †RDH   | 250 | -      | 100 | -       | 30  | -       | ns   |

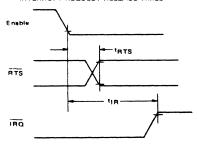

| Interrupt Request Release Time (See Figure 6)              |                  | t+R    | -   | 1.2    | -   | 0.9     | -   | 0.7     | μS   |

| Request-to-Send Delay Time (See Figure 6)                  |                  | 'RTS   | -   | 560    | -   | 480     | -   | 400     | ns   |

| Input Rise and Fall Times for 10% of the pulse width if si | maller)          | tr, tr | -   | 1.0    | -   | 0.5     | -   | 0.25    | μ5   |

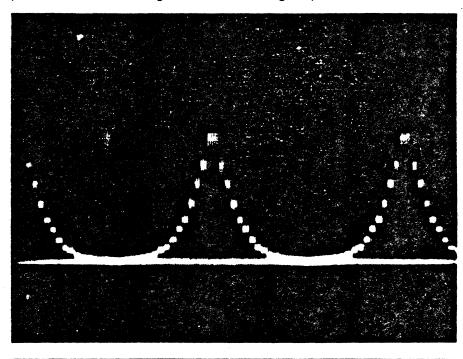

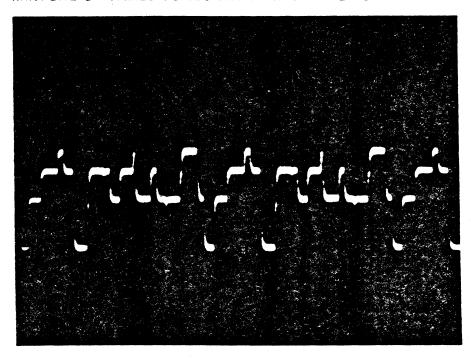

FIGURE 1 - CLOCK PULSE WIDTH, LOW-STATE

FIGURE 2 - CLOCK PULSE WIDTH, HIGH-STATE

FIGURE 3 - TRANSMIT DATA OUTPUT DELAY

FIGURE 4 - RECEIVE DATA SETUP TIME (+1 Mode)

FIGURE 5 — RECEIVE DATA HOLD TIME (+1 Mode)

FIGURE 6 — REQUEST-TO-SEND DELAY AND INTERRUPT-REQUEST RELEASE TIMES

Note: Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

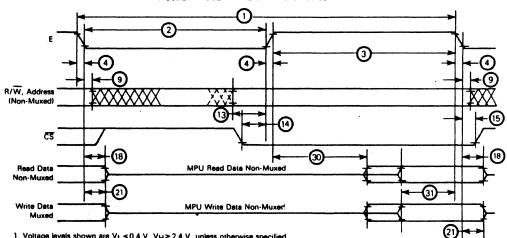

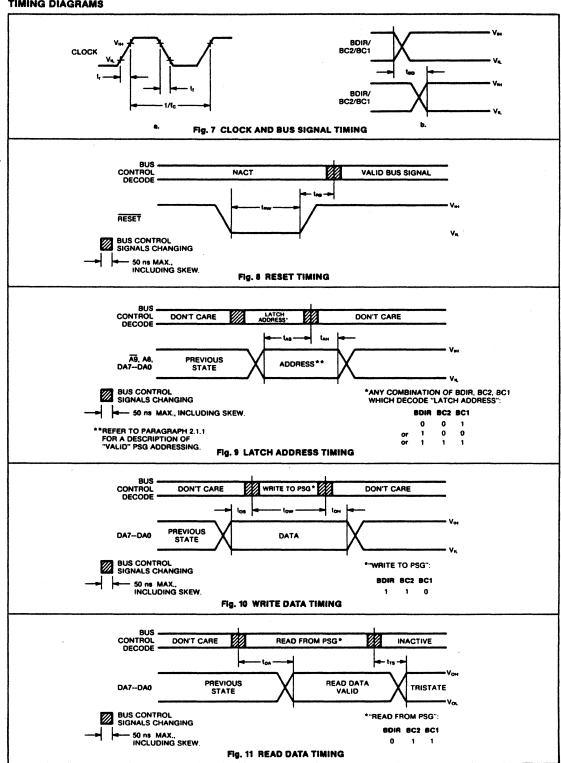

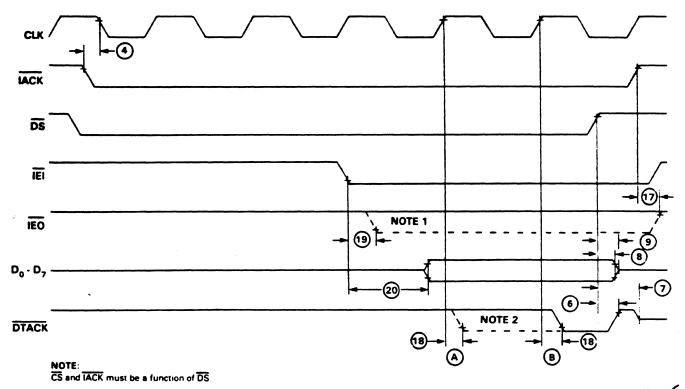

| BLIS TIMING | CHARACTERISTICS     | (See Notes  | 1 and 2 and Figure 7) |

|-------------|---------------------|-------------|-----------------------|

| DANIMII COG | CHARAC I ENIG I ICO | 1266 140(62 | i anu z anu rigule // |

| Ident.<br>Number | Characteristic                  | C                | MC8850 |      | MC88A50 |      | MC68B60 |      |      |

|------------------|---------------------------------|------------------|--------|------|---------|------|---------|------|------|

|                  | Characteristic                  | Symbol           | Min    | Max  | Min     | Max  | Min     | Mex  | Unit |

| 1                | Cycle Time                      | tcyc             | 1.0    | 10   | 0.67    | 10   | 0.5     | 10   | μS   |

| 2                | Pulse Width, E Low              | PWEL             | 430    | 9600 | 280     | 9600 | 210     | 9500 | ns   |

| 3                | Pulse Width, E High             | PWEH             | 450    | 9500 | 280     | 9600 | 220     | 9500 | ns   |

| 4                | Clock Rise and Fall Time        | ty, ty           | -      | 25   | -       | 25   | -       | 20   | ns   |

| 9                | Address Hold Time               | †AH              | 10     | -    | 10      | -    | 10      | -    | ns   |

| 13               | Address Setup Time Before E     | 1AS              | 80     | -    | 60      | -    | 40      | -    | ns   |

| 14               | Chip Select Setup Time Before E | ¹cs              | 80     | -    | 60      | -    | 40      | -    | ns   |

| 15               | Chip Select Hold Time           | ſСН              | 10     | -    | 10      | -    | 10      | -    | ns   |

| 18               | Read Data Hold Time             | <sup>1</sup> DHR | 20     | 100  | 20      | 100  | 20      | 100  | ns   |

| 21               | Write Data Hold Time            | WHQ <sup>†</sup> | 10     | -    | 10      | -    | 10      | -    | ns   |

| 30               | Output Data Delay Time          | *DDR             | -      | 290  | -       | 180  | -       | 150  | ns   |

| 31               | Input Data Setup Time           | tosw             | 165    | _    | 80      | -    | 60      | -    | ns   |

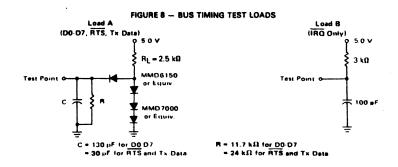

- 1. Voltage levels shown are V<sub>L</sub>  $\leq$  0.4 V, V<sub>H</sub>  $\geq$  2.4 V, unless otherwise specified 2. Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

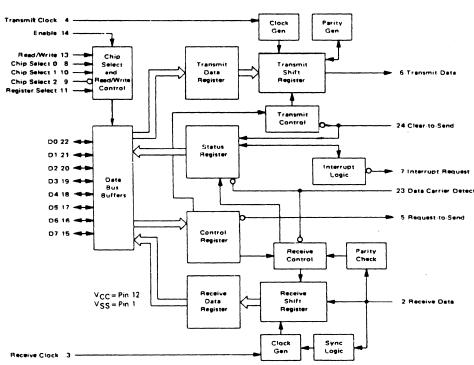

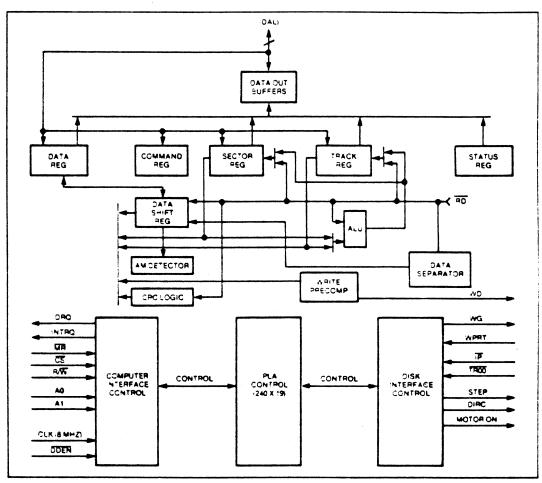

FIGURE 9 - EXPANDED BLOCK DIAGRAM

#### **DEVICE OPERATION**

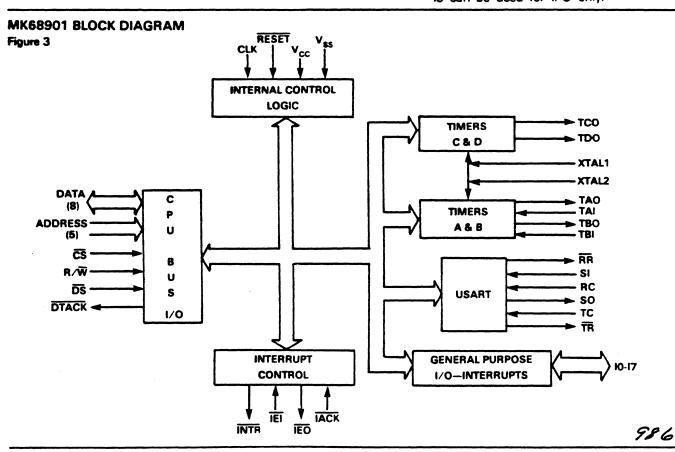

At the bus interface, the ACIA appears as two addressable memory locations. Internally, there are four registers: two read-only and two write-only registers. The read-only registers are Status and Receive Data; the write-only registers are Control and Transmit Data. The serial interface consists of serial input and output lines with independent clocks, and three peripheral/modem control lines.

#### POWER ON/MASTER RESET

The master reset (CR0, CR1) should be set during system initialization to insure the reset condition and prepare for programming the ACIA functional configuration when the communications channel is required. During the first master reset, the IRQ and RTS outputs are held at level 1. On all other master resets, the RTS output can be programmed high or low with the IRQ output held high. Control bits CR5 and CR6 should also be programmed to define the state of RTS whenever master reset is utilized. The ACIA also contains internal power-on reset logic to detect the power line turn-on transition and hold the chip in a reset state to prevent erroneous output transitions prior to initialization. This circuitry depends on clean power turn-on transitions. The

power-on reset is released by means of the bus-programmed master reset which must be applied prior to operating the ACIA. After master resetting the ACIA, the programmable Control Register can be set for a number of options such as variable clock divider ratios, variable word length, one or two stop bits, parity (even, odd, or none), etc.

#### **TRANSMIT**

A typical transmitting sequence consists of reading the ACIA Status Register either as a result of an interrupt or in the ACIA's turn in a polling sequence. A character may be written into the Transmit Data Register if the status read operation has indicated that the Transmit Data Register is empty. This character is transferred to a Shift Register where it is serialized and transmitted from the Transmit Data output preceded by a start bit and followed by one or two stop bits. Internal parity (odd or even) can be optionally added to the character and will occur between the last data bit and the first stop bit. After the first character is written in the Data Register, the Status Register can be read again to check for a Transmit Data Register Empty condition and current peripheral status. If the register is empty, another character can be loaded for transmission even though the first character is in the process of being transmitted (because of double buffering). The second character will be automatically transferred into the Shift Register when the first character transmission is completed. This sequence continues until all the characters have been transmitted.

#### RECEIVE

Data is received from a peripheral by means of the Receive Data input. A divide-by-one clock ratio is provided for an externally synchronized clock (to its data) while the divideby-16 and 64 ratios are provided for internal synchronization. Bit synchronization in the divide-by-16 and 64 modes is initiated by the detection of 8 or 32 low samples on the receive line in the divide-by-16 and 64 modes respectively. False start bit deletion capability insures that a full half bit of a start bit has been received before the internal clock is synchronized to the bit time. As a character is being received, parity (odd or even) will be checked and the error indication will be available in the Status Register along with framing error, overrun error, and Receive Data Register full. In a typical receiving sequence, the Status Register is read to determine if a character has been received from a peripheral. If the Receiver Data Register is full, the character is placed on the 8-bit ACIA bus when a Read Data command is received from the MPU. When parity has been selected for a 7-bit word (7 bits plus parity), the receiver strips the parity bit (D7 = 0) so that data alone is transferred to the MPU. This feature reduces MPU programming. The Status Register can continue to be read to determine when another character is available in the Receive Data Register. The receiver is also double buffered so that a character can be read from the data register as another character is being received in the shift register. The above sequence continues until all characters have been received.

#### INPUT/OUTPUT FUNCTIONS

#### ACIA INTERFACE SIGNALS FOR MPU

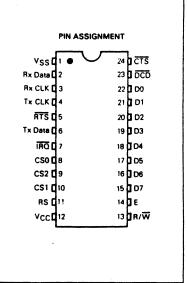

The ACIA interfaces to the M6800 MPU with an 8-bit bidirectional data bus, three chip select lines, a register select line, an interrupt request line, read/write line, and enable line. These signals permit the MPU to have complete control over the ACIA.

ACIA Bidirectional Data (D0-D7) — The bidirectional data lines (D0-D7) allow for data transfer between the ACIA and the MPU. The data bus output drivers are three-state devices that remain in the high-impedance (off) state except when the MPU performs an ACIA read operation.

ACIA Enable (E) — The Enable signal, E, is a high-impedance TTL-compatible input that enables the bus input/output data buffers and clocks data to and from the ACIA. This signal will normally be a derivative of the MC6800 ¢2 Clock or MC6800 E clock.

Read/Write  $(R/\overline{W})$  — The Read/Write line is a high-impedance input that is TTL compatible and is used to control the direction of data flow through the ACIA's input/out-put data bus interface. When Read/Write is high (MPU Read cycle), ACIA output drivers are turned on and a selected register is read. When it is low, the ACIA output drivers are

turned off and the MPU writes into a selected register. Therefore, the Read/Write signal is used to select read-only or write-only registers within the ACIA.

Chip Select (CS0, CS1, CS2) — These three high-impedance TTL-compatible input lines are used to address the ACIA. The ACIA is selected when CS0 and CS1 are high and CS2 is low. Transfers of date to and from the ACIA are then performed under the control of the Enable Signal, Read/Write, and Register Select.

Register Select (RS) — The Register Select line is a high-impedance input that is TTL compatible. A high level is used to select the Transmit/Receive Data Registers and a low level the Control/Status Registers. The Read/Write signal line is used in conjunction with Register Select to select the read-only or write-only register in each register pair.

Interrupt Request ( $\overline{IRQ}$ ) — Interrupt Request is a TTL-compatible, open-drain (no internal pullup), active low output that is used to interrupt the MPU. The  $\overline{IRQ}$  output remains low as long as the cause of the interrupt is present and the appropriate interrupt enable within the ACIA is set. The  $\overline{IRQ}$  status bit, when high, indicates the  $\overline{IRQ}$  output is in the active state.

Interrupts result from conditions in both the transmitter and receiver sections of the ACIA. The transmitter section causes an interrupt when the Transmitter Interrupt Enabled condition is selected (CR5•CR6), and the Transmit Data Register Empty (TDRE) status bit is high. The TDRE status bit indicates the current status of the Transmitter Data Register except when inhibited by Clear-to-Send (CTS) being high or the ACIA being maintained in the Reset condition. The interrupt is cleared by writing data into the Transmit Data Register. The interrupt is masked by disabling the Transmitter Interrupt via CR5 or CR6 or by the loss of CTS which inhibits the TDRE status bit. The Receiver section causes an interrupt when the Receiver Interrupt Enable is set and the Receive Data Register Full (RDRF) status bit is high, an Overrun has occurred, or Data Carrier Detect (DCD) has gone high. An interrupt resulting from the RDRF status bit can be cleared by reading data or resetting the ACIA. Interrupts caused by Overrun or loss of DCD are cleared by reading the status register after the error condition has occurred and then reading the Receive Data Register or resetting the ACIA. The receiver interrupt is masked by resetting the Receiver Interrupt Enable.

#### **CLOCK INPUTS**

Separate high-impedance TTL-compatible inputs are provided for clocking of transmitted and received data. Clock frequencies of 1, 16, or 64 times the data rate may be selected.

**Transmit Clock (Tx CLK)** — The Transmit Clock input is used for the clocking of transmitted data. The transmitter initiates data on the negative transition of the clock.

Receive Clock (Rx CLK) — The Receive Clock input is used for synchronization of received data. (In the  $\pm 1$  mode, the clock and data must be synchronized externally.) The receiver samples the data on the positive transition of the clock

#### SERIAL INPUT/OUTPUT LINES

Receive Data (Rx Data) — The Receive Data line is a high-impedance TTL-compatible input through which data is received in a serial format. Synchronization with a clock for detection of data is accomplished internally when clock rates of 16 or 64 times the bit rate are used.

Transmit Data (Tx Data) — The Transmit Data output line transfers serial data to a modern or other peripheral.

#### PERIPHERAL/MODEM CONTROL

The ACIA includes several functions that permit limited control of a peripheral or modem. The functions included are Clear-to-Send, Request-to-Send and Data Carrier Detect.

Clear-to-Send (CTS) — This high-impedance TTL-compatible input provides automatic control of the transmitting end of a communications link via the modem Clear-to-Send active low output by inhibiting the Transmit Data Register Empty (TDRE) status bit.

Request-to-Send (RTS) — The Request-to-Send output enables the MPU to control a peripheral or modern via the data bus. The RTS output corresponds to the state of the Control Register bits CR5 and CR6. When CR6=0 or both CR5 and CR6=1, the RTS output is low (the active state). This output can also be used for Data Terminal Ready (DTR).

Data Carrier Detect (DCD) — This high-impedance TTL-compatible input provides automatic control, such as in the receiving end of a communications link by means of a modern Data Carrier Detect output. The DCD input inhibits and initializes the receiver section of the ACIA when high. A low-to-high transition of the Data Carrier Detect initiates an interrupt to the MPU to indicate the occurrence of a loss of carrier when the Receive Interrupt Enable bit is set. The Rx CLK must be running for proper DCD operation.

#### ACIA REGISTERS

The expanded block diagram for the ACIA indicates the internal registers on the chip that are used for the status, control, receiving, and transmitting of data. The content of each of the registers is summarized in Table 1.

#### TRANSMIT DATA REGISTER (TDR)

Data is written in the Transmit Data Register during the negative transition of the enable (E) when the ACIA has been addressed with RS high and R/W low. Writing data into the register causes the Transmit Data Register Empty bit in the Status Register to go low. Data can then be transmitted, if the transmitter is idling and no character is being transmitted, then the transfer will take place within 1-bit time of the trailing edge of the Write command. If a character is being transmitted, the new data character will commence as soon as the previous character is complete. The transfer of data causes the Transmit Data Register Empty (TDRE) bit to indicate empty.

#### RECEIVE DATA REGISTER (RDR)

Data is automatically transferred to the empty Receive Data Register (RDR) from the receiver deserializer (a shift register) upon receiving a complete character. This event causes the Receive Data Register Full bit (RDRF) in the status buffer to go high (full). Data may then be read through the bus by addressing the ACIA and selecting the Receive Data Register with RS and R/W high when the ACIA is enabled. The non-destructive read cycle causes the RDRF bit to be cleared to empty although the data is retained in the RDR. The status is maintained by RDRF as to whether or not the data is current. When the Receive Data Register is full, the automatic transfer of data from the Receiver Shift Register to the Data Register is inhibited and the RDR contents remain valid with its current status stored in the Status Register.

TABLE 1 - DEFINITION OF ACIA REGISTER CONTENTS

|                               | Buffer Address                           |                                         |                                  |                                        |  |  |  |

|-------------------------------|------------------------------------------|-----------------------------------------|----------------------------------|----------------------------------------|--|--|--|

| Data<br>Bus<br>Line<br>Number | RS • R/W<br>Transmit<br>Data<br>Register | RS • R/W<br>Receive<br>Data<br>Register | RS • R/W<br>Control<br>Register  | ŘŠ + R/W<br>Status<br>Register         |  |  |  |

|                               | (Write Only)                             | (Read Only)                             | (Write Only)                     | (Read Only)                            |  |  |  |

| 0                             | Data Bit 0"                              | Data Bit 0                              | Counter Divide<br>Select 1 (CRO) | Receive Data Register Full (RORF)      |  |  |  |

| 1                             | Data Bit 1                               | Data Bit 1                              | Counter Divide<br>Select 2 (CR1) | Transmit Data Register<br>Empty (TDRE) |  |  |  |

| 2                             | Data Bit 2                               | Data Bit 2                              | Word Select 1<br>(CR2)           | Data Carrier Detect<br>(DCD)           |  |  |  |

| 3                             | Date Bit 3                               | Data Bit 3                              | Word Select 2<br>(CR3)           | Clear to Send<br>(CTS)                 |  |  |  |

| 4                             | Data Bit 4                               | Data Bit 4                              | Word Select 3<br>(CR4)           | Framing Error<br>(FE)                  |  |  |  |

| 5                             | Date Bit 5                               | Data Bit 5                              | Transmit Control 1<br>(CR5)      | Receiver Overrun<br>(OVRN)             |  |  |  |

| 6                             | Date Bit 6                               | Data Bit 6                              | Transmit Control 2<br>(CR6)      | Parity Error (PE)                      |  |  |  |

| ,                             | Data Bit 7***                            | Data Bit 7**                            | Receive Interrupt Enable (CR7)   | Interrupt Request                      |  |  |  |

<sup>\*</sup> Leading bit LSB Bit 0

<sup>\*\*</sup> Data bit will be zero in 7 bit plus parity modes

\*\*\* Data bit is 'don't care' in 7 bit plus parity modes

#### CONTROL REGISTER

The ACIA Control Register consists of eight bits of write-only buffer that are selected when RS and  $R/\overline{W}$  are low. This register controls the function of the receiver, transmitter, interrupt enables, and the Request-to-Send peripheral/modern control output.

Counter Divide Select Bits (CR0 and CR1) — The Counter Divide Select Bits (CR0 and CR1) determine the divide ratios utilized in both the transmitter and receiver sections of the ACIA. Additionally, these bits are used to provide a master reset for the ACIA which clears the Status Register (except for external conditions on CTS and DCD) and initializes both the receiver and transmitter. Master reset does not affect other Control Register bits. Note that after power-on or a power fail/restart, these bits must be set high to reset the ACIA. After resetting, the clock divide ratio may be selected. These counter select bits provide for the following clock divide ratios:

| CR1 | CRO | Function     |

|-----|-----|--------------|

| 0   | 0   | +1           |

| 0   | 1   | + 16         |

| 1   | 0   | +64          |

| 1   | 1 1 | Master Reset |

Word Select Bits (CR2, CR3, and CR4) — The Word Select bits are used to select word length, parity, and the number of stop bits. The encoding format is as follows:

| CR4 | CR3 | CR2 | Function                           |

|-----|-----|-----|------------------------------------|

| 0   | 0   | 0   | 7 Bits + Even Parity + 2 Stop Bits |

| 0   | 0   | 1   | 7 Bits + Odd Parity + 2 Stop Bits  |

| 0   | 1   | 0   | 7 Bits + Even Parity + 1 Stop Bit  |

| 0   | 1   | 1   | 7 Bits + Odd Parity + 1 Stop Bit   |

| 1   | 0   | 0   | 8 Bits + 2 Stop Bits               |

| 1   | 0   | 1   | 8 Bits + 1 Stop Bit                |

| 1   | 1   | 0   | 8 Bits + Even parity + 1 Stop Bit  |

| 1   | 1   | 1   | 8 Bits + Odd Parity + 1 Stop Bit   |

Word length, Parity Select, and Stop Bit changes are not buffered and therefore become effective immediately.

Transmitter Control Bits (CR5 and CR6) — Two Transmitter Control bits provide for the control of the interrupt from the Transmit Data Register Empty condition, the Request-to-Send (RTS) output, and the transmission of a Break level (space). The following encoding format is used:

| CR6 | CR5 | Function                                     |

|-----|-----|----------------------------------------------|

| ٥   | 0   | RTS = low, Transmitting Interrupt Disabled.  |

| 0   | 1   | RTS = low, Transmitting Interrupt Enabled.   |

| 1   | 0   | RTS = high, Transmitting Interrupt Disabled. |

| 1   | 1   | RTS = low, Transmits a Break level on the    |

|     |     | Transmit Data Output. Transmitting Inter-    |

|     |     | rupt Disabled.                               |

Receive Interrupt Eneble Bit (CR7) — The following interrupts will be enabled by a high level in bit position 7 of the Control Register (CR7): Receive Data Register Full, Overrun, or a low-to-high transition on the Data Carrier Detect (DCD) signal line.

#### STATUS REGISTER

Information on the status of the ACIA is available to the MPU by reading the ACIA Status Register. This read-only register is selected when RS is low and R/W is high. Information stored in this register indicates the status of the Transmit Data Register, the Receive Data Register and error logic, and the peripheral/modem status inputs of the ACIA.

Receive Data Register Full (RDRF), Bit 0 — Receive Data Register Full indicates that received data has been transferred to the Receive Data Register. RDRF is cleared after an MPU read of the Receive Data Register or by a master reset. The cleared or empty state indicates that the contents of the Receive Data Register are not current. Data Carrier Detect being high also causes RDRF to indicate empty.

Transmit Data Register Empty (TDRE), Bit 1 — The Transmit Data Register Empty bit being set high indicates that the Transmit Data Register contents have been transferred and that new data may be entered. The low state indicates that the register is full and that transmission of a new character has not begun since the last write data command.

Data Carrier Detect (DCD), Bit 2 — The Data Carrier Detect bit will be high when the DCD input from a modem has gone high to indicate that a carrier is not present. This bit going high causes an Interrupt Request to be generated when the Receive Interrupt Enable is set. It remains high after the DCD input is returned low until cleared by first reading the Status Register and then the Data Register or until a master reset occurs. If the DCD input remains high after read status and read data or master reset has occurred, the interrupt is cleared, the DCD status bit remains high and will follow the DCD input.

Clear-to-Send (CTS), Bit 3 — The Clear-to-Send bit indicates the state of the Clear-to-Send input from a modem. A low CTS indicates that there is a Clear-to-Send from the modem. In the high state, the Transmit Data Register Empty bit is inhibited and the Clear-to-Send status bit will be high. Master reset does not affect the Clear-to-Send status bit.

Framing Error (FE), Bit 4 — Framing error indicates that the received character is improperly framed by a start and a stop bit and is detected by the absence of the first stop bit. This error indicates a synchronization error, faulty transmission, or a break condition. The framing error flag is set or reset during the receive data transfer time. Therefore, this error indicator is present throughout the time that the associated character is available.

Receiver Overrun (OVRN), Bit 5 — Overrun is an error flag that indicates that one or more characters in the data stream were lost. That is, a character or a number of characters were received but not read from the Receive Data Register (RDR) prior to subsequent characters being received. The overrun condition begins at the midpoint of the last bit of the second character received in succession without a read of the RDR having occurred. The Overrun does not occur in the Status Register until the valid character prior to Overrun has

# MC6850 • MC68A50 • MC68B50

been read. The RDRF bit remains set until the Overrun is reset. Character synchronization is maintained during the Overrun condition. The Overrun indication is reset after the reading of data from the Receive Data Register or by a Master Reset.

Parity Error (PE), Bit 6 — The parity error flag indicates that the number of highs (ones) in the character does not agree with the preselected odd or even parity. Odd parity is defined to be when the total number of ones is odd. The parity error indication will be present as long as the data

character is in the RDR. If no parity is selected, then both the transmitter parity generator output and the receiver partiy check results are inhibited.

Interrupt Request ( $\overline{IRQ}$ ), Bit 7 — The  $\overline{IRQ}$  bit indicates the state of the  $\overline{IRQ}$  output. Any interrupt condition with its applicable enable will be indicated in this status bit. Anytime the  $\overline{IRQ}$  output is low the  $\overline{IRQ}$  bit will be high to indicate the interrupt or service request status.  $\overline{IRQ}$  is cleared by a read operation to the Receive Data Register or a write operation to the Transmit Data Register.

#### **OPERATION**

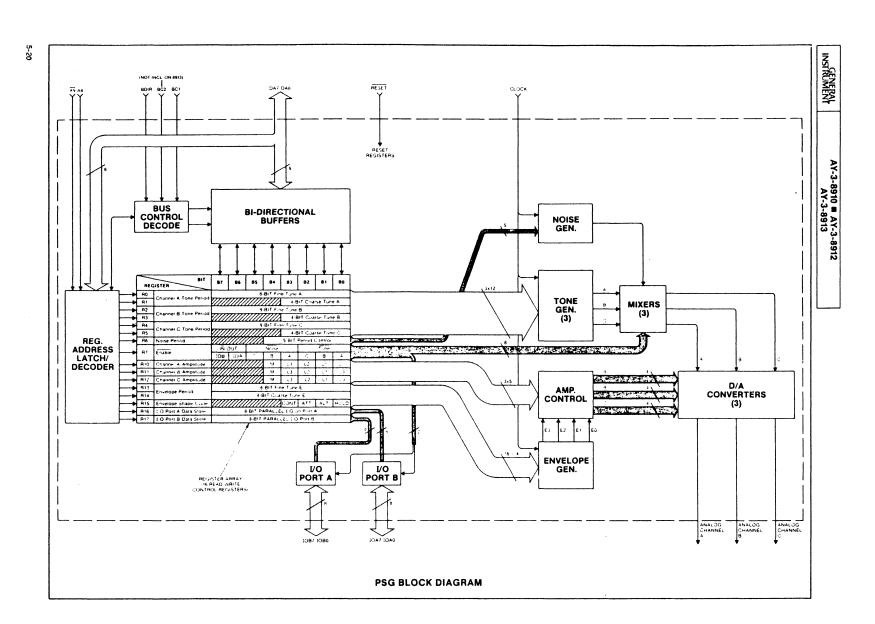

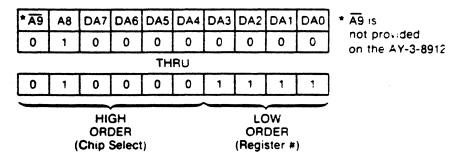

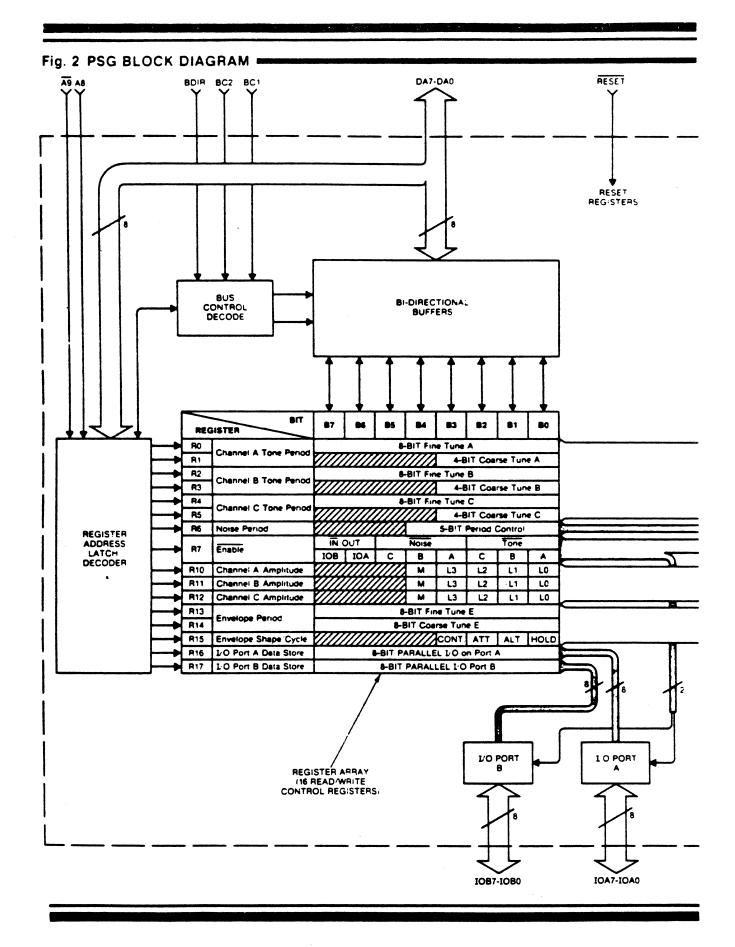

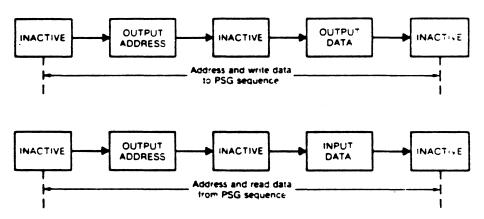

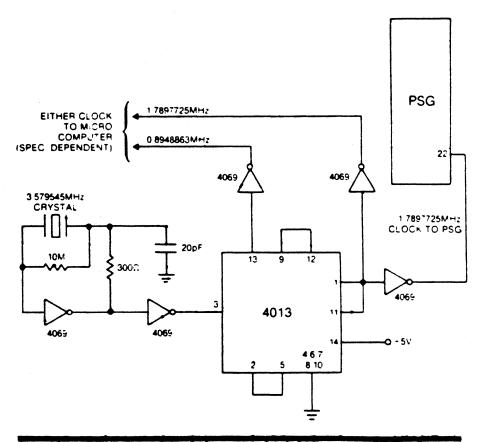

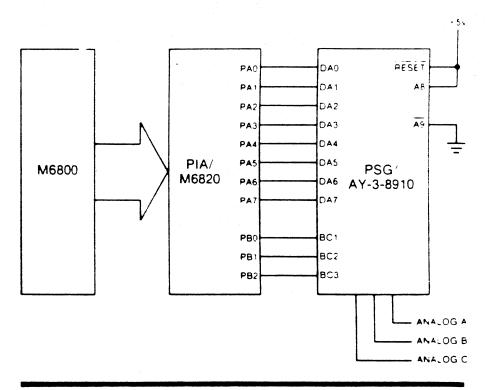

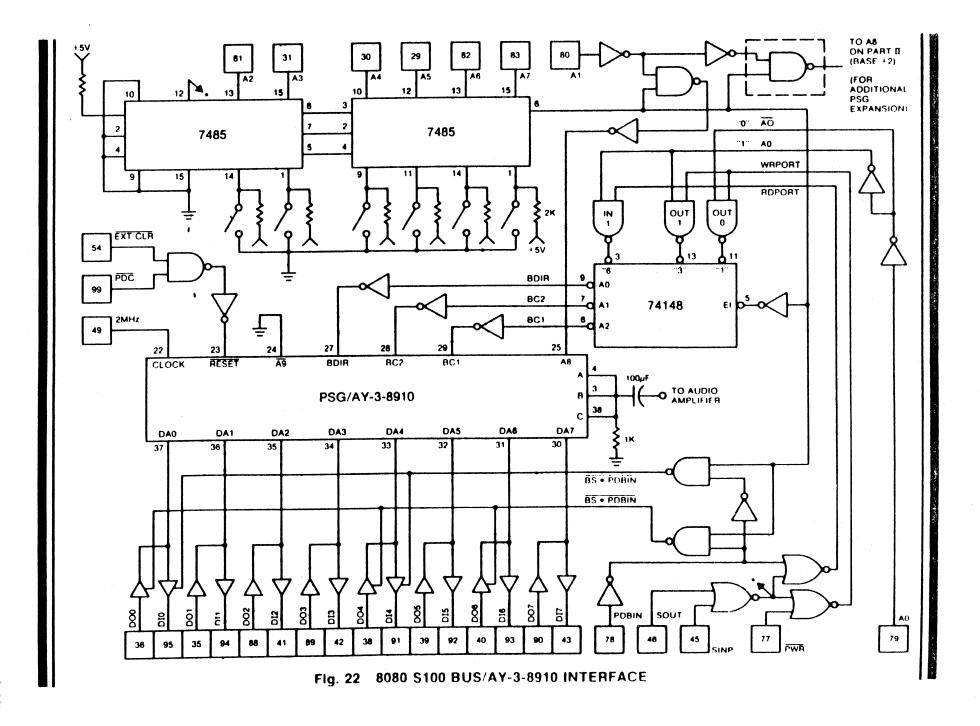

Since all functions of the PSG are controlled by the processor via a series of register loads, a detailed description of the PSG operation can best be accomplished by relating each PSG function to the control of its corresponding register. The function of creating or programming a specific sound or sound effect logically follows the control sequence listed:

| Operation               | Registers | Function                                              |

|-------------------------|-----------|-------------------------------------------------------|

| Tone Generator Control  | R0R5      | Program tone periods.                                 |

| Noise Generator Control | R6        | Program noise period.                                 |

| Mixer Control           | R7        | Enable tone and/or noise on selected channels.        |

| Amplitude Control       | R10R12    | Select "fixed" or "envelope-<br>variable" amplitudes. |

| Envelope Generator      | R13R15    | Program envelope period                               |

| Control                 |           | and select envelope pattern                           |

#### **Tone Generator Control**

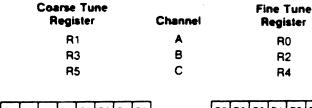

(Registers R0, R1, R2, R3, R4, R5)

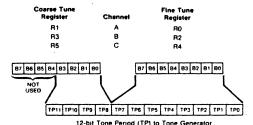

The frequency of each square wave generated by the three Tone Generators (one each for Channels A, B, and C) is obtained in the PSG by first counting down the input clock by 16, then by further counting down the result by the programmed 12-bit Tone Period value. Each 12-bit value is obtained in the PSG by combining the contents of the relative Coarse and Fine Tune registers, as illustrated in the following:

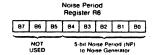

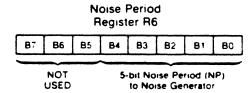

# Noise Generator Control (Register R6)

The frequency of the noise source is obtained in the PSG by first counting down the input clock by 16, then by further counting down the result by the programmed 5-bit Noise Period value. This 5-bit value consists of the lower 5 bits (B4--B0) of register R6, as illustrated in the following:

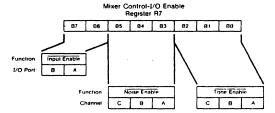

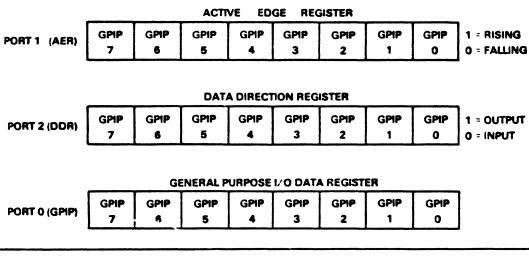

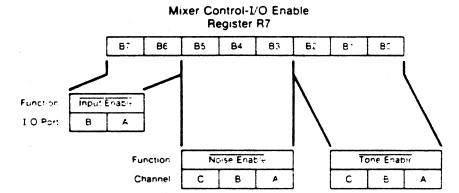

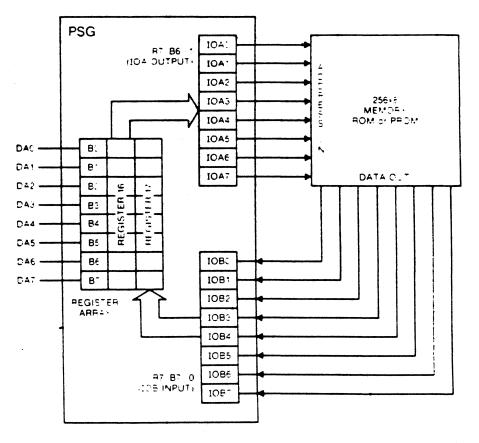

# Mixer Control-I/O Enable (Register R7)

Register R7 is a multi-function Enable register which controls the three Noise/Tone Mixers and the two general purpose I/O Ports.

The Mixers, as previously described, combine the noise and tone frequencies for each of the three channels. The determination of combining neither/either/both noise and tone frequencies on each channel is made by the state of bits B5--B0 of R7.

The direction (input or output) of the two general purpose I/O Ports (IOA and IOB) is determined by the state of bits B7 and B6 of R7.

These functions are illustrated in the following:

#### AY-3-8910 = AY-3-8912 AY-3-8913

GENERAL

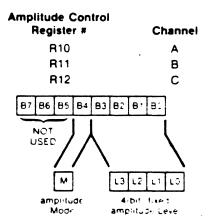

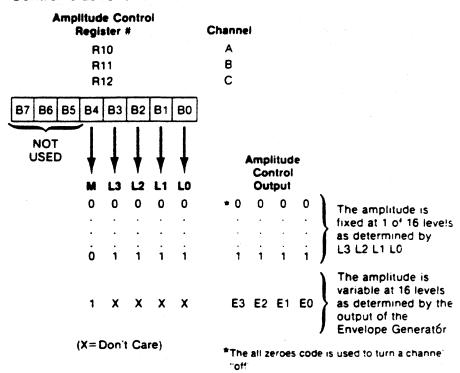

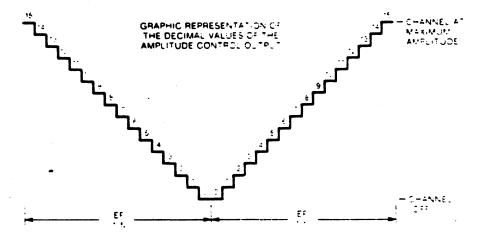

#### Amplitude Control (Registers R10, R11, R12)

The amplitudes of the signals generated by each of the three D/A Converters (one each for Channels A, B, and C) is determined by the contents of the lower 5 bits (B4--B0) of registers R10, R11, and R12 as illustrated in the following:

# Envelope Generator Control (Registers R13, R14, R15)

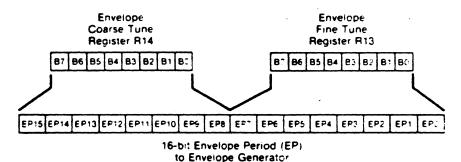

To accomplish the generation of fairly complex envelope patterns, two independent methods of control are provided in the PSG. first, is possible to vary the frequency of the envelope using registers R13 and R14; and second, the relative shape and cycle pattern of the envelope can be varied using register R15. The following paragraphs explain the details of the envelope control functions, describing first the envelope period control and then the envelope shape/cycle control.

#### ENVELOPE PERIOD CONTROL (Registers R13, R14)

The frequency of the envelope is obtained in the PSG by first counting down the input clock by 256, then by further counting down the result by the programmed 16-bit Envelope Period value. This 16-bit value is obtained in the PSG by combining the contents of the Envelope Coarse and Fine Tune registers, as illustrated in the following:

16-bit Envelope Period (EP) to Envelope Generator

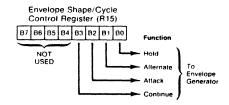

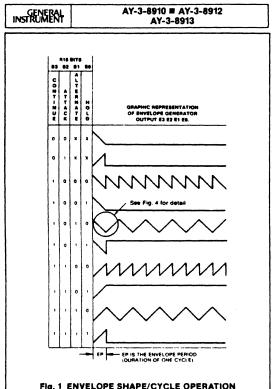

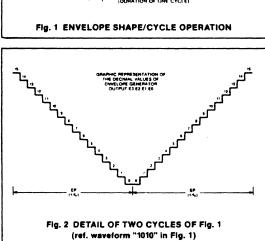

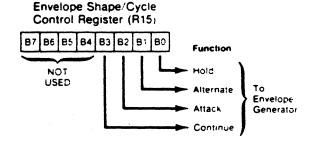

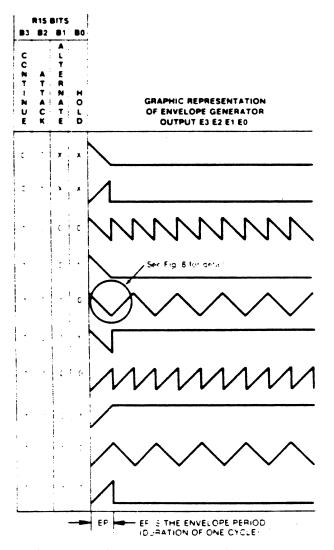

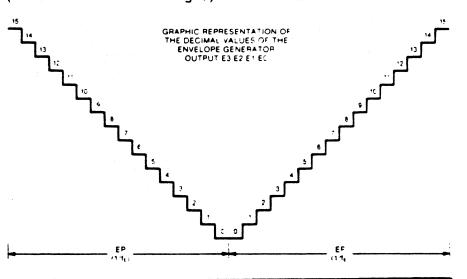

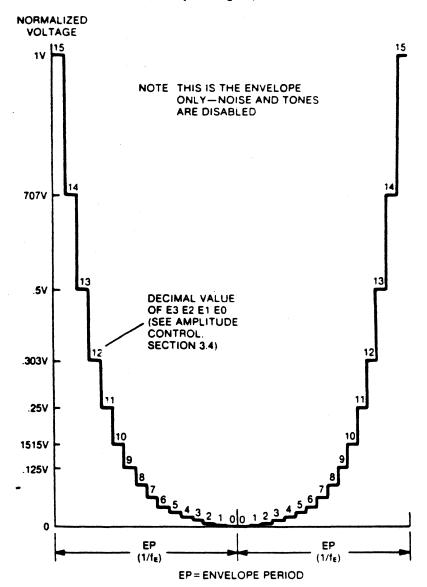

#### ENVELOPE SHAPE/CYCLE CONTROL (Register R15)

The Envelope Generator further counts down the envelope frequency by 16, producing a 16-state per cycle envelope pattern as defined by its 4-bit counter output, E3 E2 E1 E0. The particular shape and cycle pattern of any desired envelope is accomplished by controlling the count pattern (count up/count down) of the 4-bit counter and by defining a single-cycle or repeat-cycle pattern.

This envelope shape/cycle control is contained in the lower 4 bits (B3--B0) of register R15. Each of these 4 bits controls a function in the envelope generator, as illustrated in the following:

5-21

#### I/O Port Data Store (Registers R16, R17)

Registers R16 and R17 function as intermediate data storage registers between the PSG/CPU data bus (DA0--DA7) and the two i/O ports (IOA7--IOA0 and IOB7--IOB0). Both ports are available in the AY-3-8910. only I/O Port A is available in the AY-3-8912 none are available on the AY-3-8913. Using registers R16 and R17 for the transfer of I/O data has no effect on sound generation.

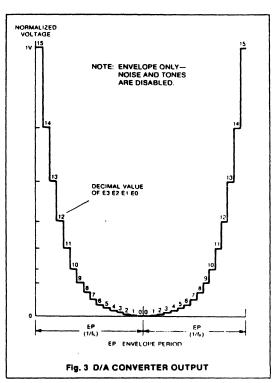

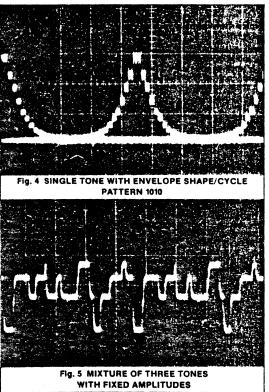

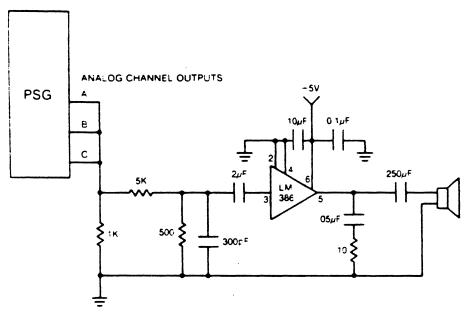

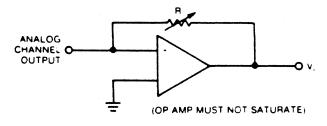

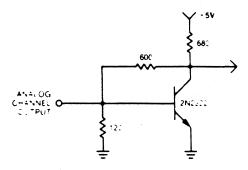

## D/A Converter Operation

Since the primary use of the PSG is to produce sound for the highly imperfect amplitude detection mechanism of the human ear, the D/A conversion is performed in logarithmic steps with a normalized voltage range of from 0 to 1 Volt. The specific amplitude control of each of the three D/A Converters is accomplished by the three sets of 4-bit outputs of the Amplitude Control block, while the Mixer outputs provide the base signal frequency (Noise and/or Tone).

### ELECTRICAL CHARACTERISTICS (AY-3-8910, AY-3-8912)

| Maximum Ratings*                           |                |

|--------------------------------------------|----------------|

| Storage Temperature                        | 55°C to +150°C |

| Operating Temperature                      | 0°C to +40°C   |

| V <sub>CC</sub> and all other input/Output |                |

| Voltages with Respect to V <sub>ss</sub>   | 0.3V to +8.0V  |

|                                            |                |

#### Standard Conditions (unless otherwise noted):

V<sub>CC</sub> = +5V ±5% V<sub>SS</sub> = GND

Operating Temperature = 0°C to +40°C

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Characteristics                             | Sym             | Min | Typ** | Max    | Units | Conditions                    |

|---------------------------------------------|-----------------|-----|-------|--------|-------|-------------------------------|

| DC CHARACTERISTICS                          |                 |     |       |        |       |                               |

| All inputs                                  | 1               |     |       |        |       |                               |

| Low Level                                   | V <sub>IL</sub> | 0   | _     | 0.6    | V     |                               |

| High Level                                  | V <sub>IH</sub> | 2.4 | _     | Vcc    | V     |                               |

| All Outputs (except Analog Channel Outputs) |                 |     |       |        |       |                               |

| Low Level                                   | Vol             | 0   | _     | 0.5    | V     | I <sub>OL</sub> = 1.6mA, 20pf |

| High Level                                  | Vон             | 2.4 | _     | Vcc    | l v   | I <sub>OH</sub> = 100µA, 20pf |

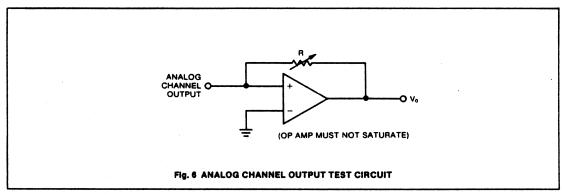

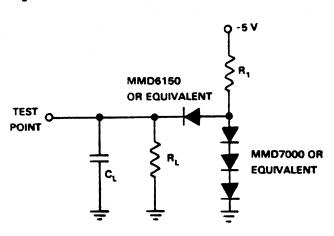

| Analog Channel Outputs                      | Vo              | 0   | _     | 60     | dB .  | Test Circuit: Fig. 6          |

| Power Supply Current                        | Icc             | -   | 45    | 85     | mA    |                               |

| AC CHARACTERISTICS                          | ľ               |     |       |        |       |                               |

| Clock Input                                 | \               | 1   |       |        |       |                               |

| Frequency                                   | fc              | 1   | _     | 2      | MHz   | 1                             |

| Rise Time                                   | tr              | _   | _     | 50     | ns    |                               |

| Fall Time                                   | tr              | -   |       | 50     | ns    | Fig. 7                        |

| Duty Cycle                                  | -               | 25  | 50    | 85     | %     | ( Fig. /                      |

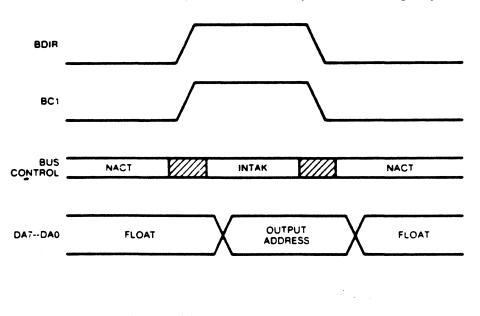

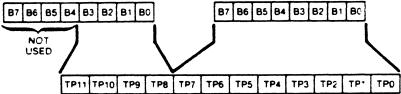

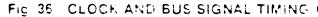

| Bus Signals (BDIR, BC2, BC1)                | - 1             | l   |       |        | 1     |                               |

| Associative Delay Time                      | teo             | -   | _     | 50     | ns    | <b>/</b>                      |

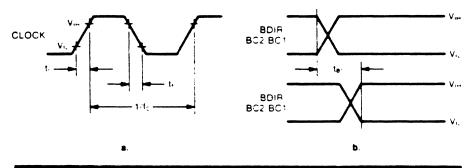

| Reset                                       | 1               | 1   | ·     |        | 1     |                               |

| Reset Pulse Width                           | law             | 500 | _     | _      | ns    | 1) 5:- 0                      |

| Reset to Bus Control Delay Time             | tee             | 100 | _     | _      | ns    | } Fig. 8                      |

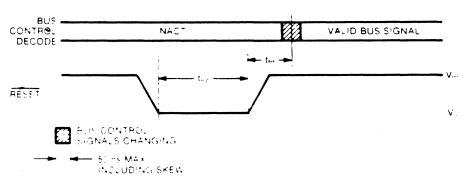

| A9, A8, DA7DA0 (Address Mode)               | ı               |     |       |        | ł     |                               |

| Address Setup Time                          | tas             | 400 | _     | _      | ns    | h = -                         |

| Address Hold Time                           | tan             | 100 | _     | _      | ns    | } Fig. 9                      |

| DA7DA0 (Write Mode)                         | 1               | l   |       |        | 1     |                               |

| Write Data Pulse Width                      | tow             | 500 | _     | 10,000 | ns    | 1)                            |

| Write Data Setup Time                       | tos             | 50  | l –   | _      | ns    | Fig. 10                       |

| Write Data Hold Time                        | tон             | 100 | -     | -      | ns    | 1)                            |

| DA7DA0 (Read Mode)                          |                 |     | 1     | l      | l     |                               |

| Read Data Access Time                       | tos             | -   | 250   | 500    | ns    | 1)                            |

| DA7DA0 (inactive Mode)                      |                 |     | l     | l      |       | Fig. 11                       |

| Tristate Delay Time                         | trs             | _   | 100   | 200    | ns    | ]]                            |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.

INSTRUMENT

AY-3-8910 = AY-3-8912 AY-3-8913

# ELECTRICAL CHARACTERISTICS (AY-3-8913)

Maximum Ratings\*

55°C to +150°C

Storage Temperature

−55°C to +150°C

Operating Temperature

0°C to +70°C

V<sub>CC</sub> and all other Input/Output Voltages with Respect to V<sub>SS</sub>

−0.3V to +8.0V

Standard Conditions (unless otherwise noted):

V<sub>CC</sub> = +5V ±5% V<sub>SS</sub> = GND Operating Temperature = 0°C to +70°C \* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Characteristics                                          | Sym               | Min  | Max  | Units | Conditions           |

|----------------------------------------------------------|-------------------|------|------|-------|----------------------|

| DC CHARACTERISTICS                                       |                   |      |      |       |                      |

| Input Voltage Levels                                     |                   | 1    |      |       |                      |

| Low Level                                                | V,L               | 0    | 0.7  | V     |                      |

| High Level                                               | · V <sub>IH</sub> | 2.2  | Vcc  | V     |                      |

| Output Voitage Levels (except<br>Analog Channel Outputs) |                   |      |      |       |                      |